Altera RapidIO II MegaCore Function User Manual

Page 103

Chapter 4: Functional Description

4–61

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

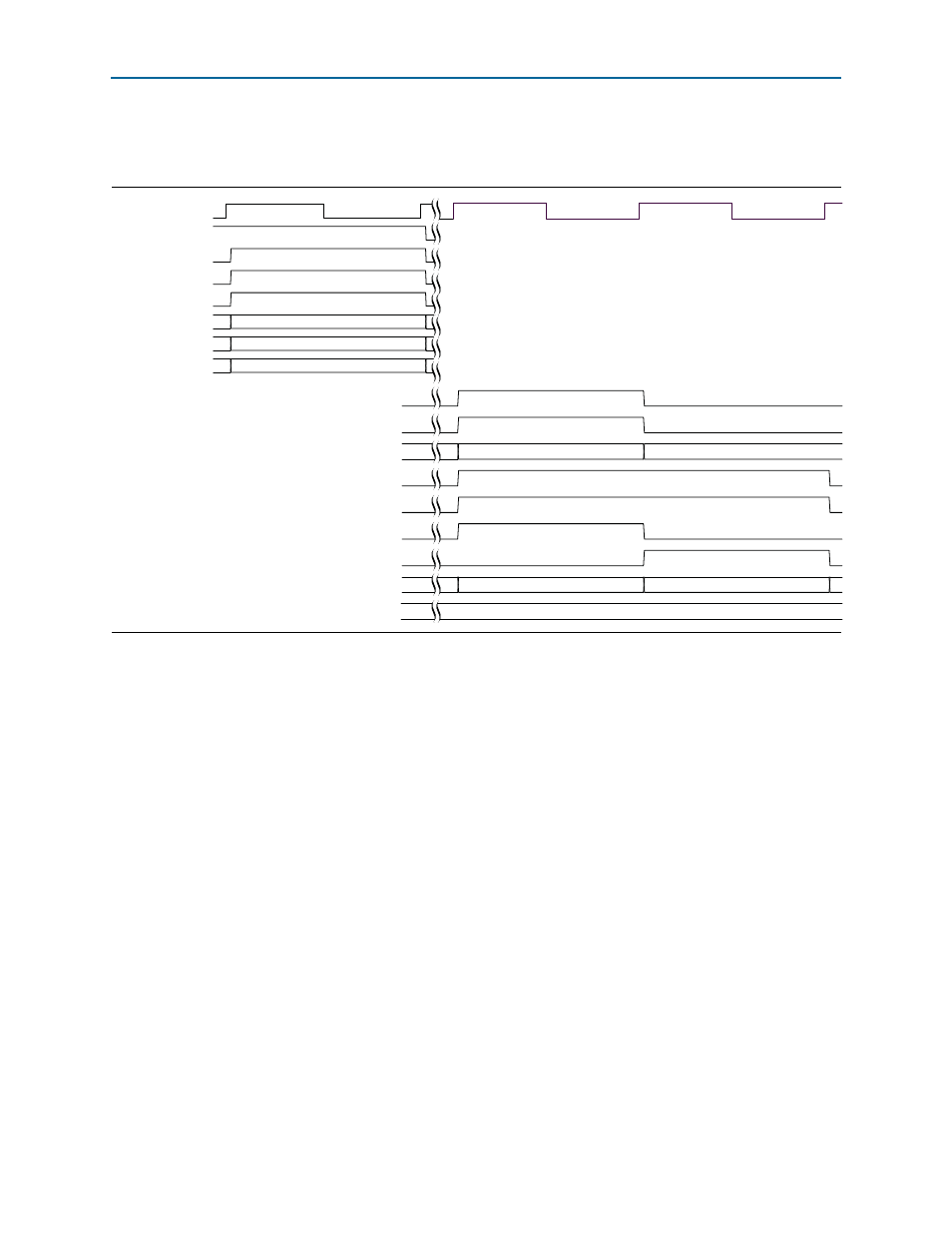

shows the behavior of the signals on the Avalon-ST pass-through

interface for this example transaction sequence.

The following two sections describe the behavior shown in

■

■

NREAD Request Transaction

In the first clock cycle of the example, the IP core asserts gen_tx_ready to indicate it is

ready to sample data. In the same cycle, user logic asserts gen_tx_valid. Because both

gen_tx_ready

and gen_tx_valid are asserted, this clock cycle is an Avalon-ST ready

cycle. The user logic provides valid data on gen_tx_data for the IP core to sample, and

asserts gen_tx_startofpacket to indicate the current value of gen_tx_data is the

initial piece of the current packet (the start of packet). On gen_tx_packet_size, user

logic reports the full length of the packet is 0xC, which is decimal 12, because the

packet comprises 12 bytes of header. The NREAD request transaction contains no

payload data.

The NREAD request requires a single clock cycle. During this clock cycle, user logic

asserts gen_tx_endofpacket and reports on gen_tx_empty that the number of empty

bytes is 4.

Figure 4–23. Avalon-ST Pass-Through Interface NREAD Request and Response Receive Example

gen_rx_hd_ready

gen_rx_hd_valid

gen_rx_hd_data[114:0]

gen_rx_pd_ready

gen_rx_pd_valid

gen_rx_pd_startofpacket

gen_rx_pd_endofpacket

gen_rx_pd_data[127:0]

gen_rx_pd_empty[2:0]

clk

gen_tx_ready

gen_tx_valid

gen_tx_empty[3:0]

gen_tx_packet_size[8:0]

gen_tx_startofpacket

gen_tx_endofpacket

0052DDDDAAAA4CBB7654321000000000

0809DAAAADDDD80BB000000000000

0123456789ABCDEFFEDCBA9876543210

00112233445566778899AABBCCDDEEFF

4

00C

gen_tx_data[127:0]

0