Altera RapidIO II MegaCore Function User Manual

Page 157

Chapter 6: Software Interface

6–19

Physical Layer Registers

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

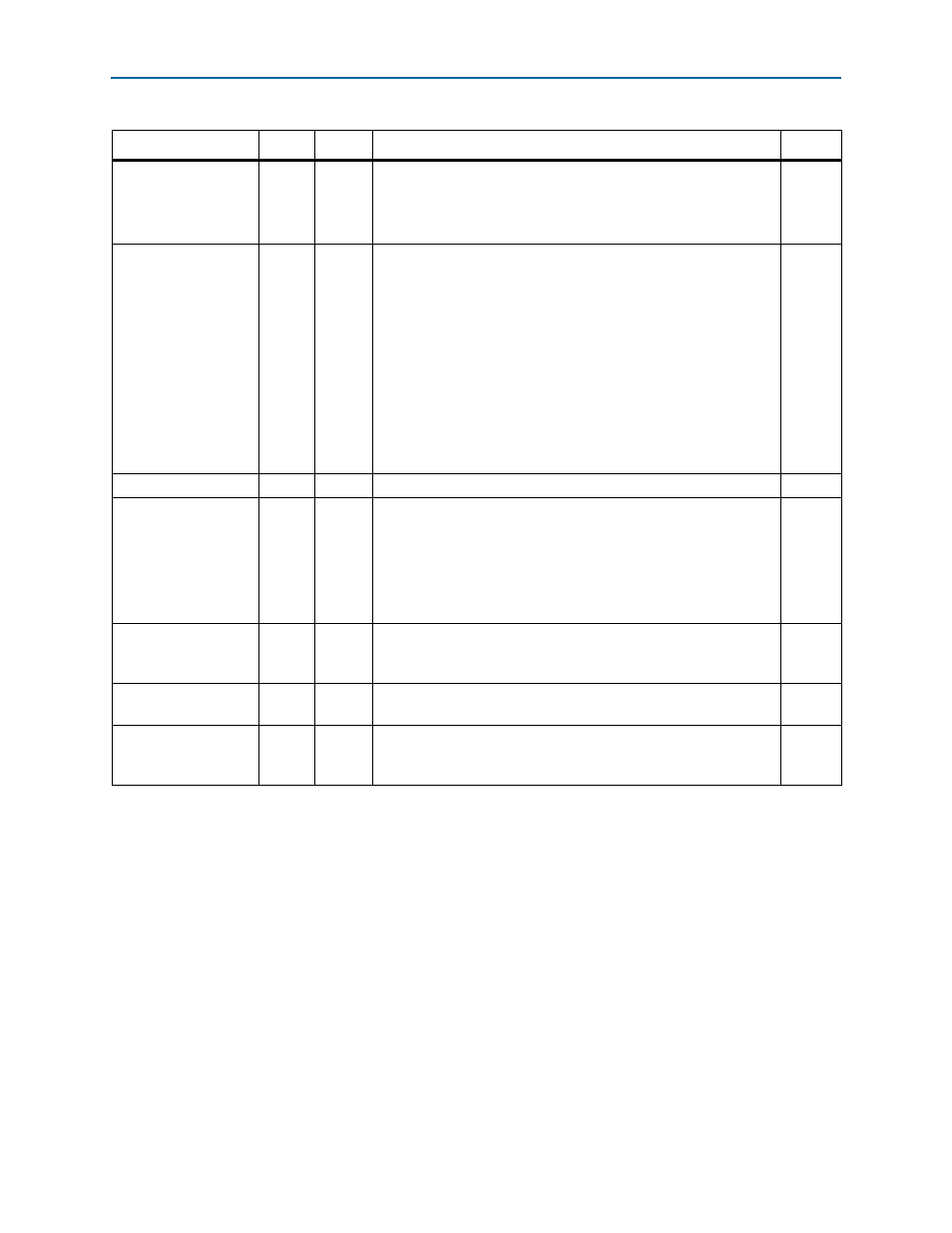

EXTENDED_PWIDTH_

OVRIDE

[15:14] RW

Together with the PWIDTH_OVRIDE field (bits [26:24] of this

register), indicates soft port configuration to control the width

modes available for port initialization.

Refer to the description of the PWIDTH_OVRIDE field.

2'b0

EXTENDED_PORT_

WIDTH

[13:12] RO

Together with the PORT_WIDTH field, indicates the hardware widths

this port supports:

Bit [13]: 8× support

1’b0: This port does not support a 8× RapidIO link.

1’b1: This port supports a 8× RapidIO link.

Bit[12]: 16× support

1’b0: This port does not support a 16× RapidIO link.

1’b1: This port supports a 16× RapidIO link.

The RapidIO II IP core does not support 8-lane or 16-lane variations,

so this field is always set to 2’b00.

2'b0

RSRV

[11:8]

RO

Reserved

4’b0

DIS_DEST_ID_CHK

[7]

RW

This bit determines whether the RapidIO II IP core checks

destination IDs in incoming request packets, or promiscuously

accepts all incoming request packets with a supported ftype. The

reset value is set in the RapidIO II parameter editor.

1'b0—Check Destination ID.

1'b1—Disable Destination ID checking.

LOG_TRANS_ERR_IRQ

_EN

[6]

RW

Controls whether an interrupt is generated when the

logical_transport_error

input signal changes from the value

of 0 to the value of 1.

1'b0

PORT_FAIL_IRQ_EN

[5]

RW

Controls whether an interrupt is generated when the port_failed

input signal changes from the value of 0 to the value of 1.

1'b0

PORT_DEGR_IRQ_EN

[4]

RW

Controls whether an interrupt is generated when the

port_degraded

input signal changes from the value of 0 to the

value of 1.

1'b0

Table 6–15. Port 0 Control CSR—Offset: 0x15C (Part 3 of 4)

Field

Bits

Access

Function

Default