Altera RapidIO II MegaCore Function User Manual

Page 73

Chapter 4: Functional Description

4–31

Logical Layer Interfaces

August 2014

Altera Corporation

RapidIO II MegaCore Function

User Guide

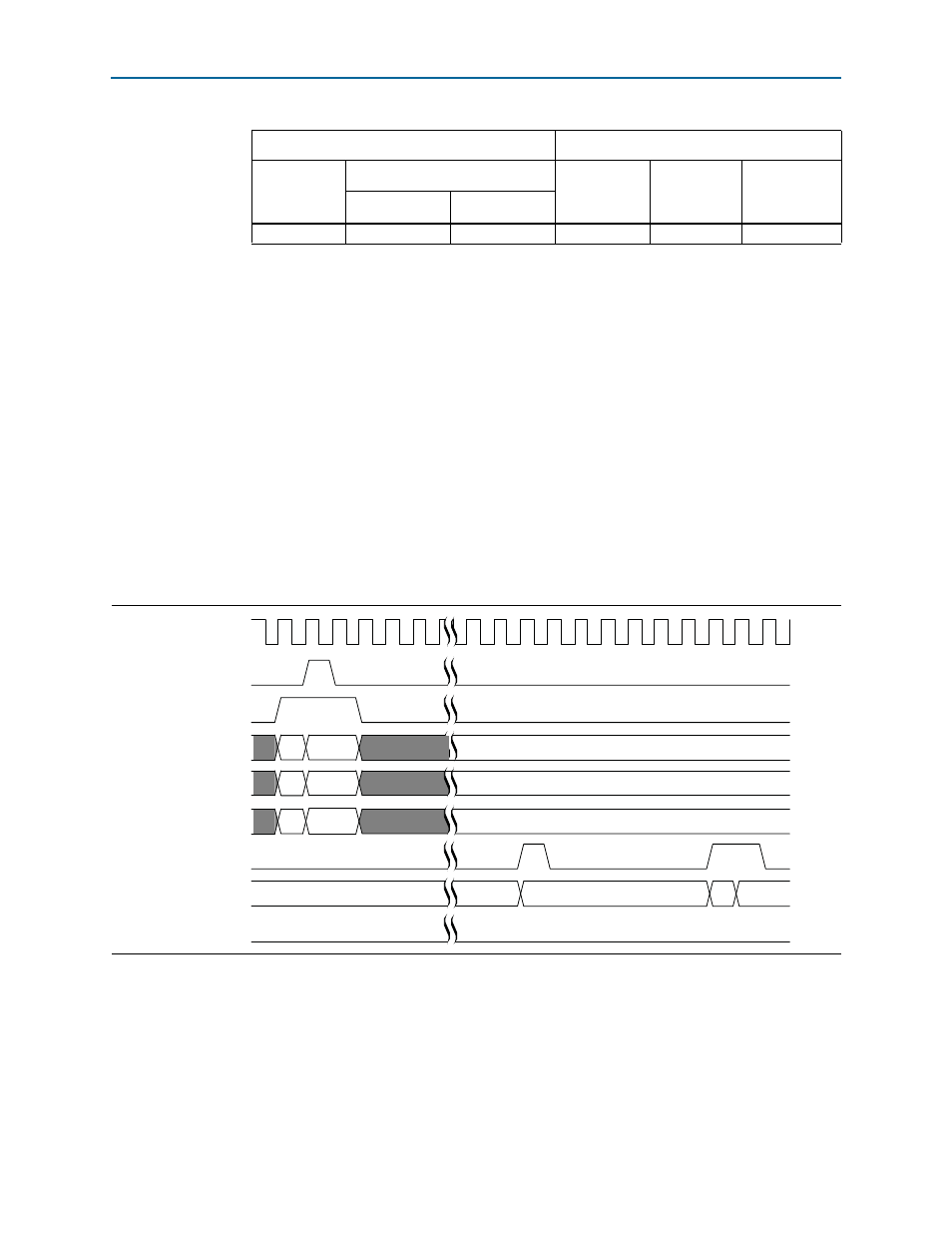

Input/Output Avalon-MM Slave Module Timing Diagrams

shows the timing dependencies on the Avalon-MM slave interface for an

outgoing RapidIO NREAD request.

shows the timing dependencies on the

Avalon-MM slave interface for an outgoing NWRITE transaction. Both transaction

requests are initiated by local user logic and appear on the Avalon-MM interface of

the slave module. The timing diagrams in

“Input/Output Avalon-MM Master

Module Timing Diagrams” on page 4–17

show the same transactions after they are

transmitted on the RapidIO link and received by an Altera RapidIO II IP core link

partner, when the RapidIO II link partner Input/Output Avalon-MM master module

sends the requests as Avalon-MM transactions.

17

FF00

00FF

1

1111

1

Note to

(1) The I/O Logical layer slave module does not handle byteenable values and byteenable-burstcount combinations

that the Avalon-MM interface does not allow. In case of an invalid byteenable or burstcount value, the RapidIO II

IP core sets the INVALID_WRITE_BYTEENABLE bit or the INVALID_WRITE_BURSTCOUNT bit (or both) of the I/O

Slave Interrupt

) if this interrupt is enabled in the I/O Slave Interrupt

Enable

register (

).

Table 4–12. I/O Logical Layer Slave Write Request Size Encoding II (Part 2 of 2)

Avalon-MM Signal Values

(1)

RapidIO Header Field Values

burstcount

(Decimal,

128-bit units)

byteenable (16'hxxxx)

wdptr

(1'bx)

wrsize

(4'bxxxx)

address[0]

(rio_addr[3])

Initial

Final

Figure 4–14. NREAD Transaction on the Input/Output Avalon-MM Slave Interface

sys_clk

ios_rd_wr_waitrequest

ios_rd_wr_read

ios_rd_wr_address[27:0]

ios_rd_wr_readdatavalid

ios_rd_wr_readdata[127:0]

ios_rd_wr_burstcount[4:0]

ios_rd_wr_readresponse

Adr0

Adr1

00000000

r0

r1

r2

01

02

ios_rd_wr_byteenable[15:0]