Achronix ACE Version 5.0 User Manual

Page 60

Editors

Chapter 3. Concepts

Reset Configuration Page

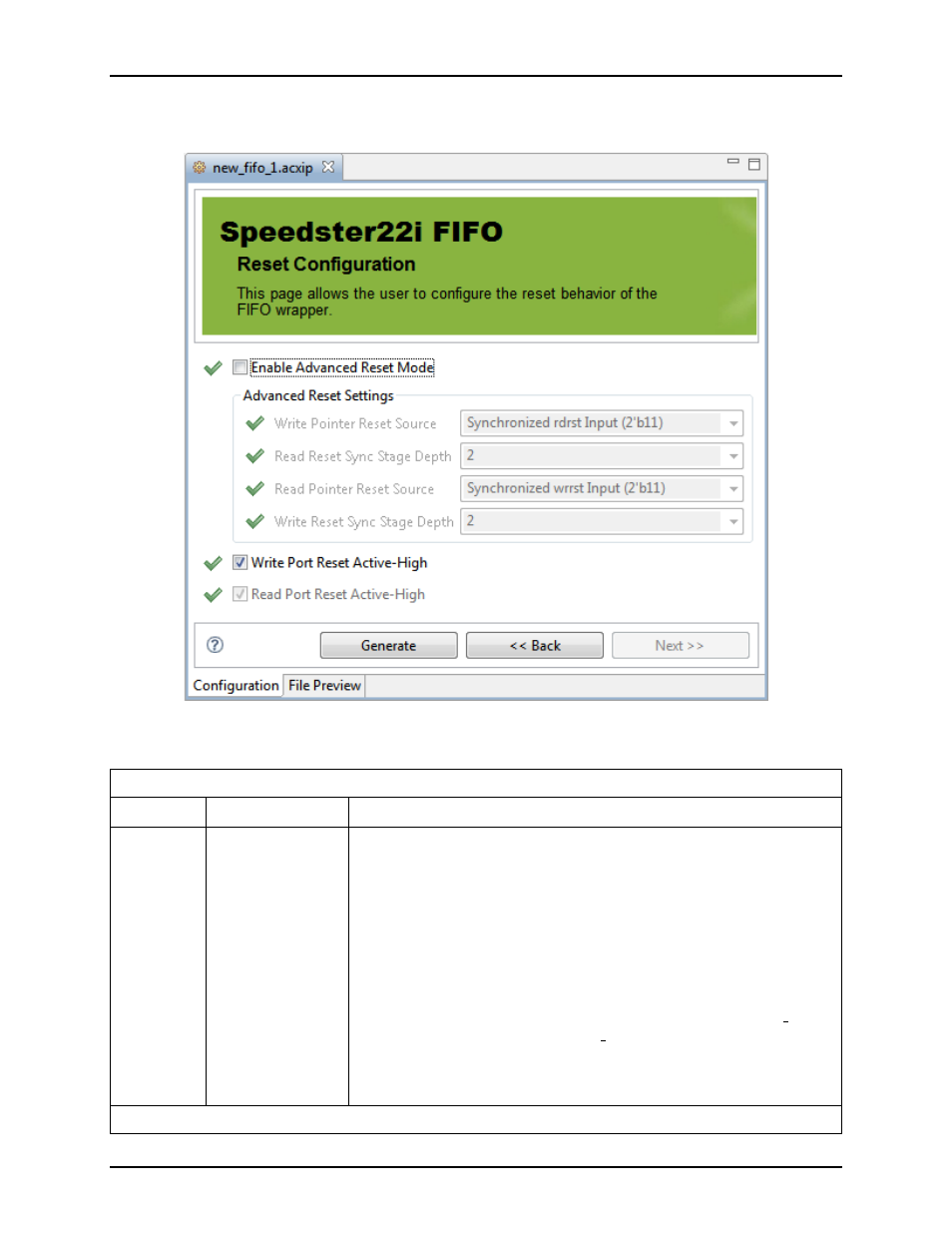

The Reset Configuration page contains the properties that govern the reset behavior of the FIFO.

Figure 3.25: FIFO IP Editor Reset Configuration Page

FIFO Editor Reset Configuration Page Options

Option

Editable

Description

Enable

Advanced

Reset

Mode

Y

When this is enabled, both the read and write port reset signals are

exposed separately and the user can configure the advanced reset

input mode and synchronization register stages. Leaving this field

unchecked will configure the FIFO to use Basic Reset Mode. In Basic

Reset Mode, only 1 reset signal is exposed to be shared between the

read and write ports. To reset the FIFO, the user will assert the reset

signal for a minimum of three clock cycles of the slower clock cycle

between the wrclk and rdclk. Asserting the reset signal clears both

the Write Pointer and Read Pointer, sets the empty and almost empty

flags, and clears the full and almost full flags. The user may then

release the reset signal. The user should not attempt to read or write

the FIFO during, or before three cycles after the deassertion of, the

reset signal.

Advanced Reset Settings

UG001 Rev. 5.0 - 5th December 2012

48