Achronix ACE Version 5.0 User Manual

Page 171

Views

Chapter 3. Concepts

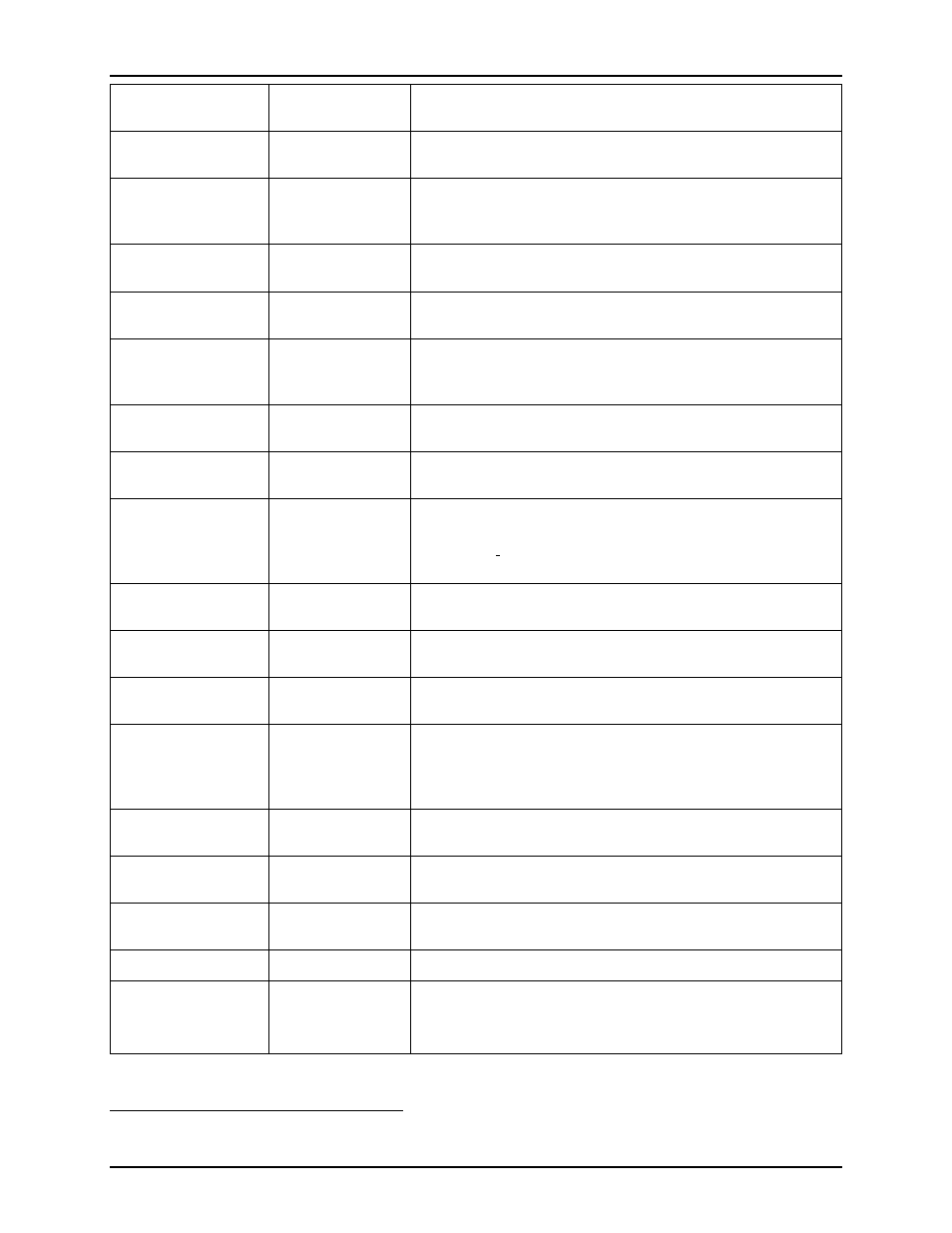

Voltage Level

The VDD voltage level for this IO, set via the IO Standard

selection.

VREF Level

The VREF voltage level for this IO, set via the IO Standard

selection.

Pad Polarity

The LVDS polarity of this IO instance in the user design.

This only applies for differential IO buffers and is set in

synthesis.

Pad DQ Capability

The DQ capability of this IO instance in the user design.

This only applies for byte lane IOs.

Site DQ Capability

The DQ capability of the site this IO instance is placed on.

This only applies for byte lane IOs.

Site DQ Domains

The list of accessible DQ Domains that can be reached from

the site this IO instance is placed on. This only applies for

byte lane IOs.

Drive Strength

Yes

The drive strength of this IO. This only applies for outputs

and inouts and a limited set of IO Standards.

Hysteresis

Yes

The hysteresis setting of this IO. This only applies for inputs

and inouts and a limited set of IO Standards.

Location

The location property can be specified in the users RTL to

do pre-placement for this IO. However, it is recommended

that the set placement constraint is used instead. This

cannot be changed in ACE after synthesis.

Open Drain

Yes

The open drain setting of this IO. This only applies for

outputs and inouts.

Slew

Yes

The slew rate of this IO. This only applies for outputs and

inouts and a limited set of IO Standards.

On Die Termination

Yes

Indicates whether on die termination is enabled for this IO.

This only applies for inputs and inouts.

Termination Value

Yes

The termination value of this IO. This only applies for

inputs and inouts and may have different ranges for

different IO Standards. On Die Termination must be turned

on for this to apply.

Keep Mode

Yes

The keep mode setting of this IO. This only applies for

inputs and inouts.

Used as Clock

Indicates whether this IO is used as a clock in the design or

not.

Used as Reset

Indicates whether this IO is used as a reset in the design or

not.

Clock Domain

The clock domain for this IO.

Target Frequency

(MHz)

Yes

The target frequency for the clock domain for this IO. This is

set via the SDC timing constraints, or is the HW limit if

unspecified.

9

This is not an electrical-only change. Editing the Ball changes the I/O placement, and requires that place and route be re-run for

the design.

159

UG001 Rev. 5.0 - 5th December 2012