Achronix ACE Version 5.0 User Manual

Page 136

Views

Chapter 3. Concepts

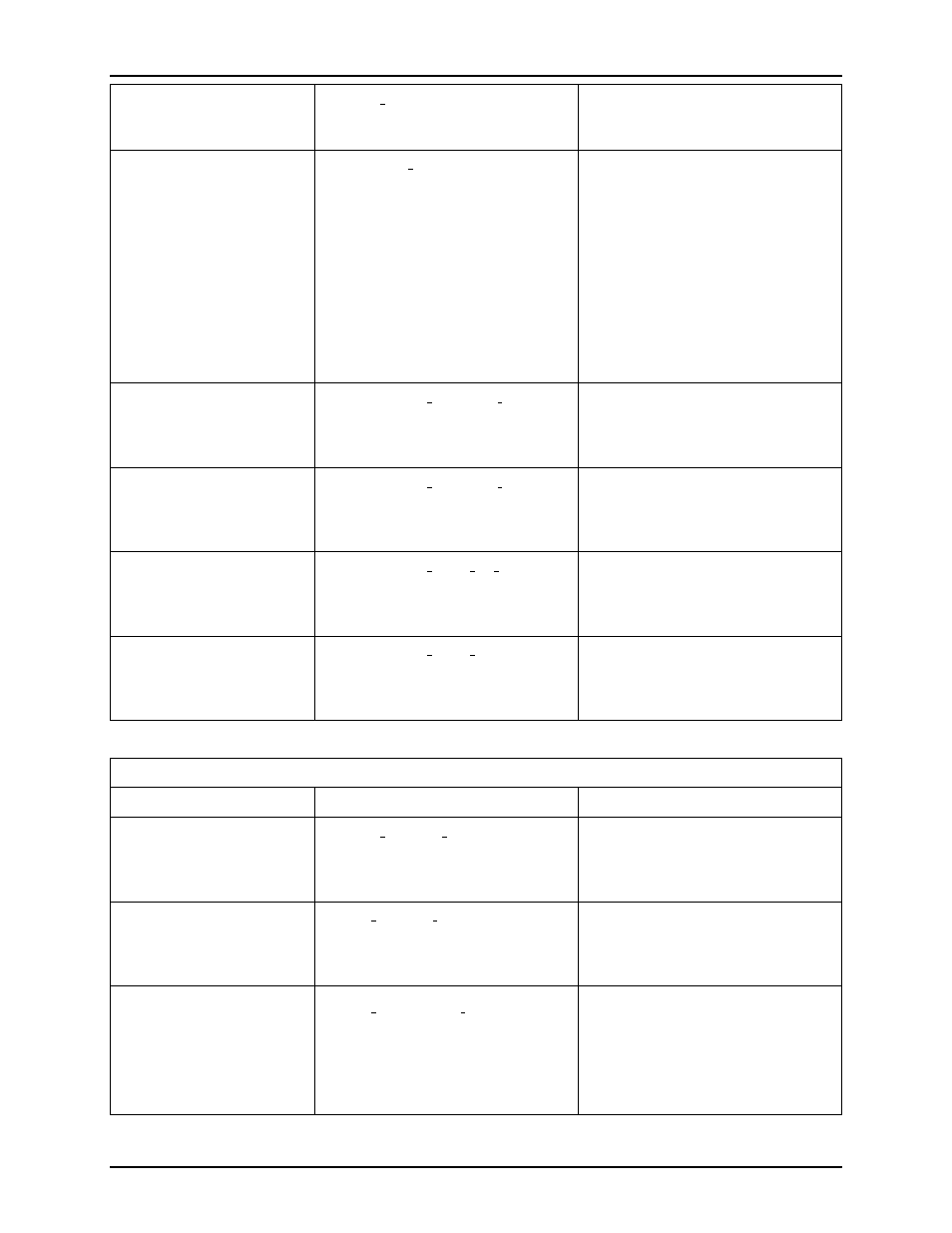

Fanout Limit

fanout limit

Specifies the net fanout limit

applied when fanout control is

enabled for this implementation.

Resynthesis Mode

synthesis remap

Specifies whether resynthesis

should optimize for timing, area, or

should be disabled. Optimizing for

area can be used to reduce the total

number of LUTs. When optimizing

for timing, the optimizations

performed will depend upon the

strategies chosen below. If the

”Place and Route” Implementation

Option ”Timing-Driven PnR” is

disabled, resynthesis timing

optimizations will also be disabled.

Rewrite Rule 1

resynthesis rewrite rule1

Specifies whether resynthesis

strategy ”Rewrite Rule 1” should

be used when Resynthesis is

optimizing for timing.

Rewrite Rule 2

resynthesis rewrite rule2

Specifies whether resynthesis

strategy ”Rewrite Rule 2” should

be used when Resynthesis is

optimizing for timing.

Move Flip-flop Reset

resynthesis move ff reset

Specifies whether resynthesis will

move flip-flop reset logic to LUTs

when Resynthesis is optimizing for

timing.

Loop Speedup

resynthesis loop speedup

Specifies whether the remapping of

critical loops in the design is

enabled when Resynthesis is

optimizing for timing.

Place and Route Implementation Options

Option

TCL Option

Description

Timing-Driven PnR

timing driven pnr

If turned on, placement and routing

will be timing-driven. Data from

timing analysis will be used to

optimize the design for high speed.

Power-Driven PnR

power driven pnr

If turned on, placement and routing

will be power-driven. Data from

power analysis will be used to

optimize the design for low power.

Post-PnR Timing

Optimization

extra placement optimization

If turned on, extended post-route

placement and routing

optimizations will be performed to

optimize timing. Using this option

will increase runtime in the routing

step.

UG001 Rev. 5.0 - 5th December 2012

124