Achronix ACE Version 5.0 User Manual

Page 23

Editors

Chapter 3. Concepts

Achieved NF

This calculated value shows the exact ”Feedback Divider

’NF’” value which will be used by the PLL. This may

differ slightly from the requested value; the closest

approximate value will be chosen if an exact match is not

possible.

Clkout Driving

External Feedback

Path

Y

Selects which of the currently-enabled clock outputs will

drive the external feedback path. Note that Phase

Adjustment is not allowed in the Feedback Path.

Enable sbus ports

Y

When selected, the sbus ports will be exposed in the

generated HDL file(s).

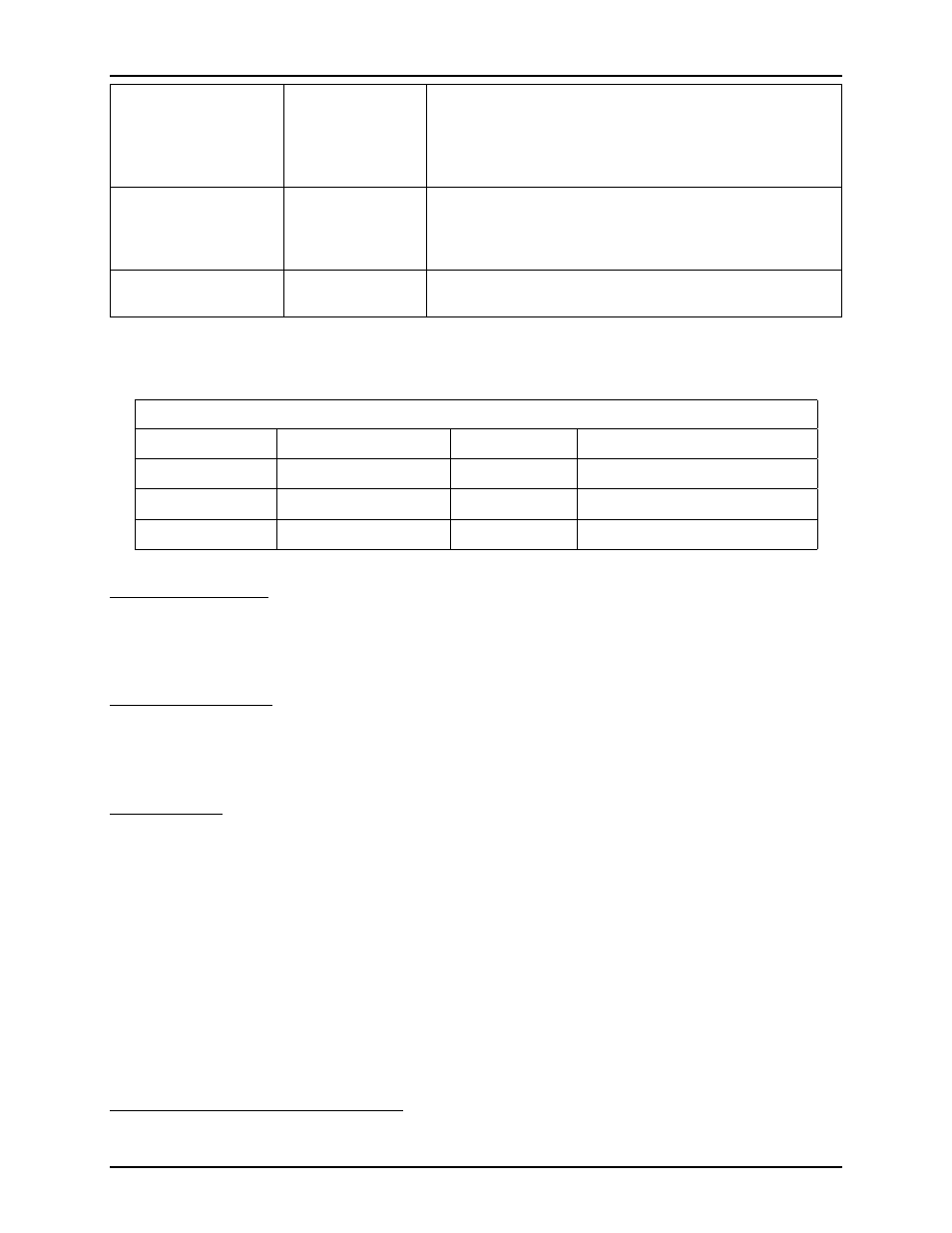

Feedback Modes

There are three feedback modes available to the PLL. Some allow fractional feedback,

others allow deskew.

PLL Feedback Modes

Mode

Fractional Feedback?

Deskew?

Algorithm

Pure Internal

Y

N

F

V CO

=(NF/NR)*F

ref

Pure External

N

Y

F

V CO

=(ODn*OSn/NR)*F

ref

Mixed

N

Y

F

V CO

=(NF*ODn*OSn/NR)*F

ref

Pure Internal Feedback

When internal feedback mode is selected, the VCO clock is divided by the ”Feedback Divider ’NF’” only.

In this mode, the PLL can have both integer and fractional feedback divider values. The ”Clkout Driving

External Feedback Path” option becomes disabled in this mode, since it is irrelevant. Deskewing is not

possible in this mode.

Pure External Feedback

When external feedback mode is selected, the VCO clock is divided by the Output Divider (ODn) and

(optionally) the Output Synthesizer (OSn). The ”Clkout Driving External Feedback Path” option becomes

enabled in this mode, and the ”Feedback Divider ’NF’” option becomes disabled. In this mode, it is not

allowed to feedback a clock output that has Phase Adjustment enabled.

4

Mixed Feedback

Mixed feedback mode is a modified version of Pure External feedback mode, in that the Feedback Divider

integer value is also in the deskew feedback path. As with Pure External mode, Phase Adjustment is not

allowed in the feedback path. The ”Clkout Driving External Feedback Path” option becomes enabled in this

mode, as does ”Feedback Divider ’NF’”.

4

Phase rotation in the feedback path will cause the PLL to unlock. If Phase Adjustment is required on any output clocks, it must be

used on outputs which are not in the feedback path.

11

UG001 Rev. 5.0 - 5th December 2012