Texas Instruments TMS320C2XX User Manual

Page 465

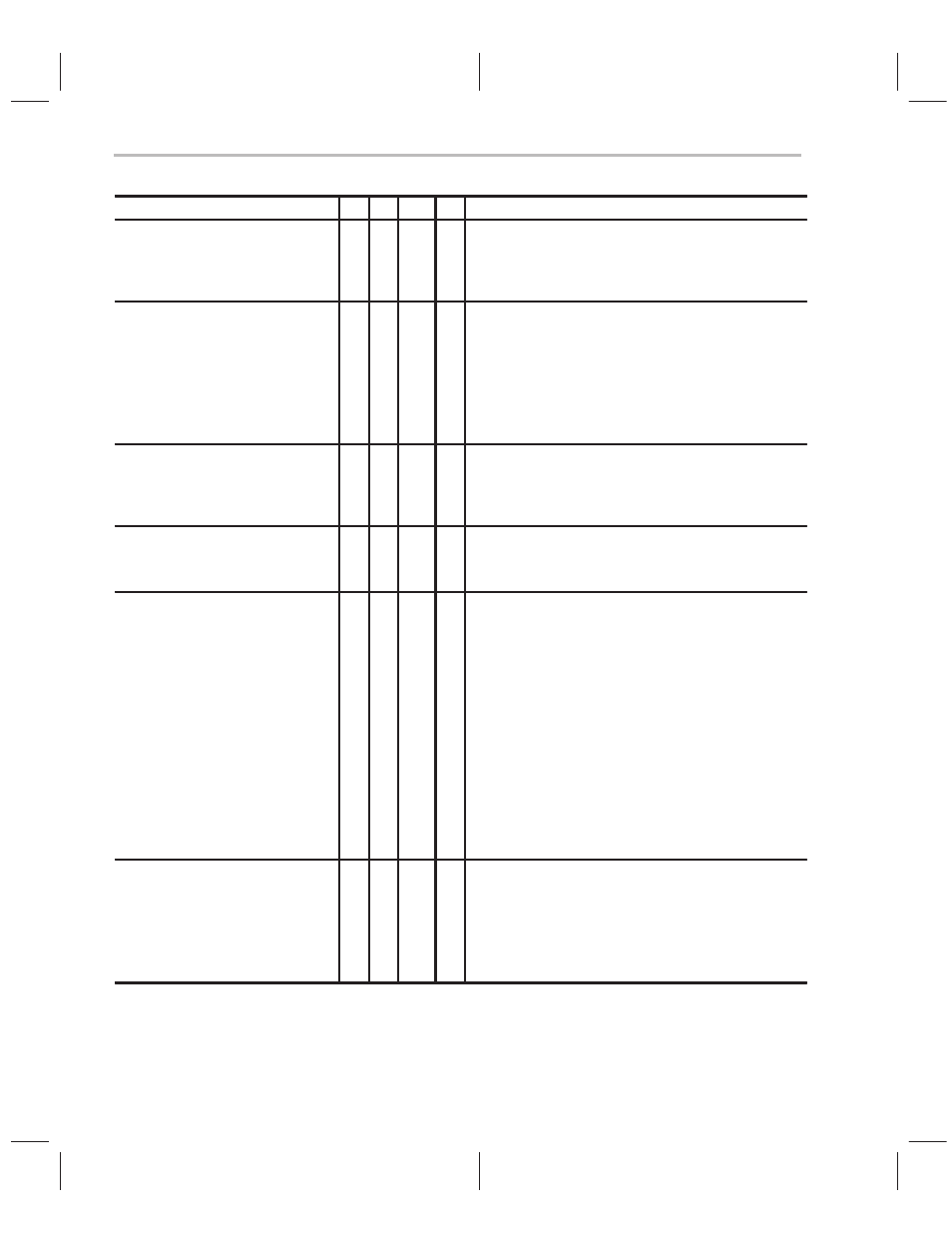

Instruction Set Comparison Table

B-16

Syntax

Description

5x

2xx

2x

1x

CC

pma, cond

1

[

, cond

2

] [, ...]

√

Call Conditionally

If the specified conditions are met, control is passed to

the pma. Not all combinations of conditions are mean-

ingful.

CC[

D] pma, cond

1

[

, cond

2

] [, ...]

√

Call Conditionally With Optional Delay

If the specified conditions are met, control is passed to

the pma. Not all combinations of conditions are mean-

ingful.

If you specify a delayed branch (CCD), the next two in-

struction words (two 1-word instructions or one 2-word

instruction) are fetched and executed before the call.

CLRC

control bit

√

√

Clear Control Bit

Set the specified control bit to a logic 0. Maskable inter-

rupts are enabled immediately after the CLRC instruc-

tion executes.

CMPL

√

√

√

Complement Accumulator

Complement the contents of the accumulator (1s com-

plement).

CMPR

CM

√

√

√

Compare Auxiliary Register With AR0

Compare the contents of the current auxiliary register

to AR0, based on the following cases:

If CM = 00

2

, test whether AR(ARP) = AR0.

If CM = 01

2

, test whether AR(ARP) < AR0.

If CM = 10

2

, test whether AR(ARP) > AR0.

If CM = 11

2

, test whether AR(ARP)

≠

AR0.

If the result is true, load a 1 into the TC status bit; other-

wise, load a 0 into the TC bit. The comparison does not

affect the tested registers.

TMS320C5x devices: Compare the contents of the

auxiliary register with the ARCR.

CNFD

√

√

√

Configure Block as Data Memory

Configure on-chip RAM block B0 as data memory.

Block B0 is mapped into data-memory locations

512h–767h.

TMS320C5x devices: Block B0 is mapped into data-

memory locations 512h–1023h.