Iack pin – Texas Instruments TMS320C2XX User Manual

Page 431

’C209 Interrupts

11-13

TMS320C209

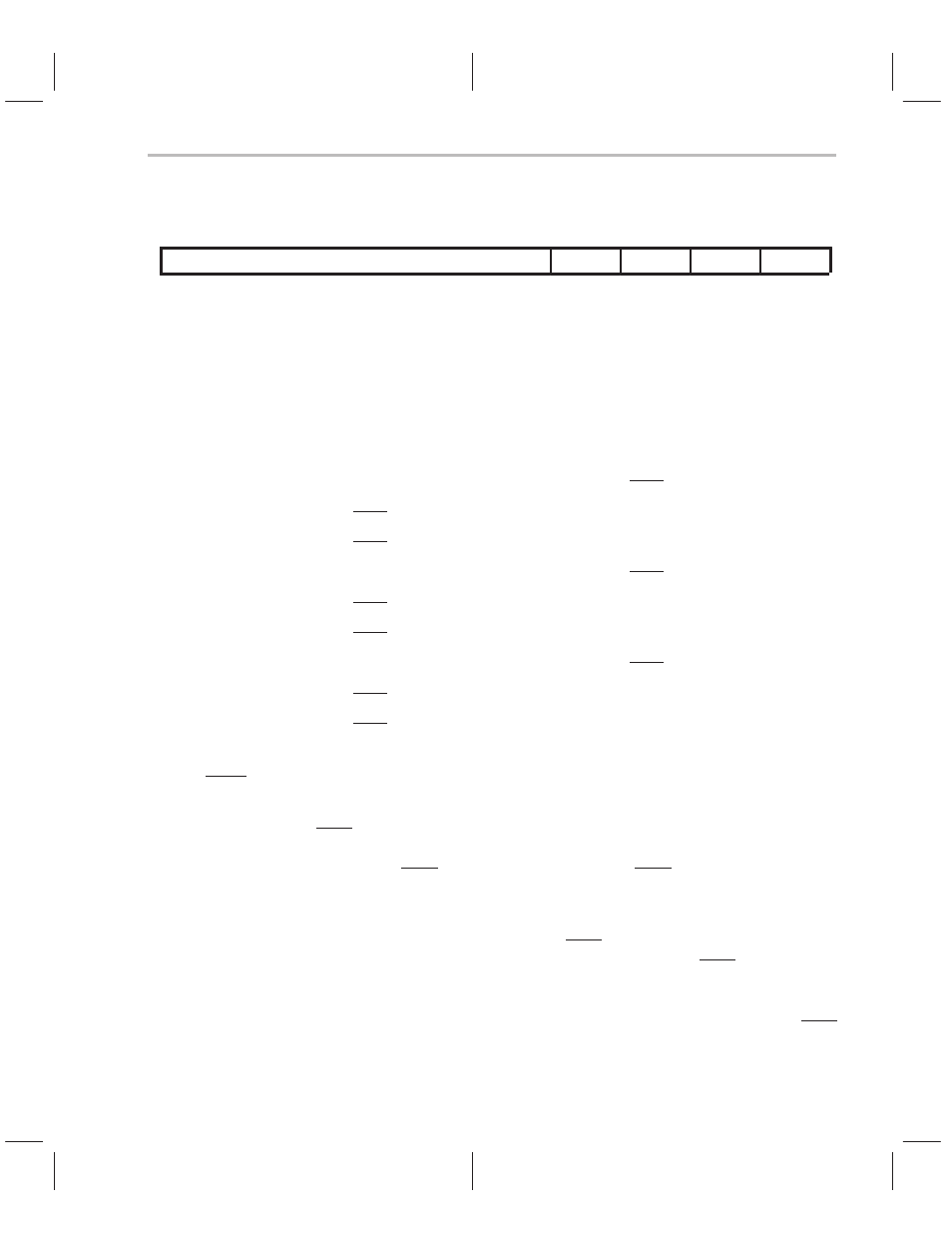

Figure 11–3.’C209 Interrupt Mask Register (IMR) — Data-Memory Address 0004h

15

4

3

2

1

0

ЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙ

ЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙЙ

Reserved

TINT

INT3

INT2

INT1

0

R/W–0

R/W–0

R/W–0

R/W–0

Note:

Note: 0 = Always read as zeros; R = Read access; W = Write access; value following dash (–) is value after reset.

Bits 15–4

Reserved. Bits 15–4 are reserved and are always read as 0s.

Bit 3

TINT — Timer interrupt mask. Mask or unmask the internal timer interrupt, TINT, with

this bit.

TINT = 0

TINT is unmasked.

TINT = 1

TINT is masked.

Bit 2

INT3 — Interrupt 3 mask. Unmask external interrupt INT3 by writing a 1 to this bit.

INT3 = 0

INT3 is unmasked.

INT3 = 1

INT3 is masked.

Bit 1

INT2 — Interrupt 2 mask. Unmask external interrupt INT2 by writing a 1 to this bit.

INT2 = 0

INT2 is unmasked.

INT2 = 1

INT2 is masked.

Bit 0

INT1 — Interrupt 1 mask. Unmask external interrupt INT1 by writing a 1 to this bit.

INT1 = 0

INT1 is unmasked.

INT1 = 1

INT1 is masked.

11.3.2 IACK Pin

On the ’C209, the interrupt acknowledge signal is available at the external

IACK pin. The CPU generates this signal while it fetches the first word of any

of the interrupt vectors, whether the interrupt was requested by hardware or

by software. IACK is not affected by wait states; IACK goes low only on the first

cycle of the read when wait states are used. At reset, the interrupt acknowl-

edge signal is generated in the same manner as for a maskable interrupt.

Your external hardware can use the IACK signal to determine when the pro-

cessor acknowledges an interrupt. Additionally, when IACK goes low, the

hardware can sample the address pins (A15–A0) to determine which interrupt

the processor is acknowledging. Since the interrupt vectors are spaced apart

by two words, address pins A1–A4 can be decoded at the falling edge of IACK

to identify the interrupt being acknowledged.