Memory and i/o spaces, Dual-access on-chip ram – Texas Instruments TMS320C2XX User Manual

Page 39

Memory and I/O Spaces

2-7

Architectural Overview

2.3

Memory and I/O Spaces

The ’C2xx memory is organized into four individually selectable spaces: pro-

gram, local data, global data, and I/O. These spaces form an address range

of 224K words.

All ’C2xx devices include 288 words of dual-access RAM (DARAM) for data

memory and 256 words of data/program DARAM. Depending on the device,

it may also have data/program single-access RAM (SARAM) and read-only

memory (ROM) or flash memory. Table 2–1 shows how much ROM, flash

memory, DARAM, and SARAM are available on the different ’C2xx devices.

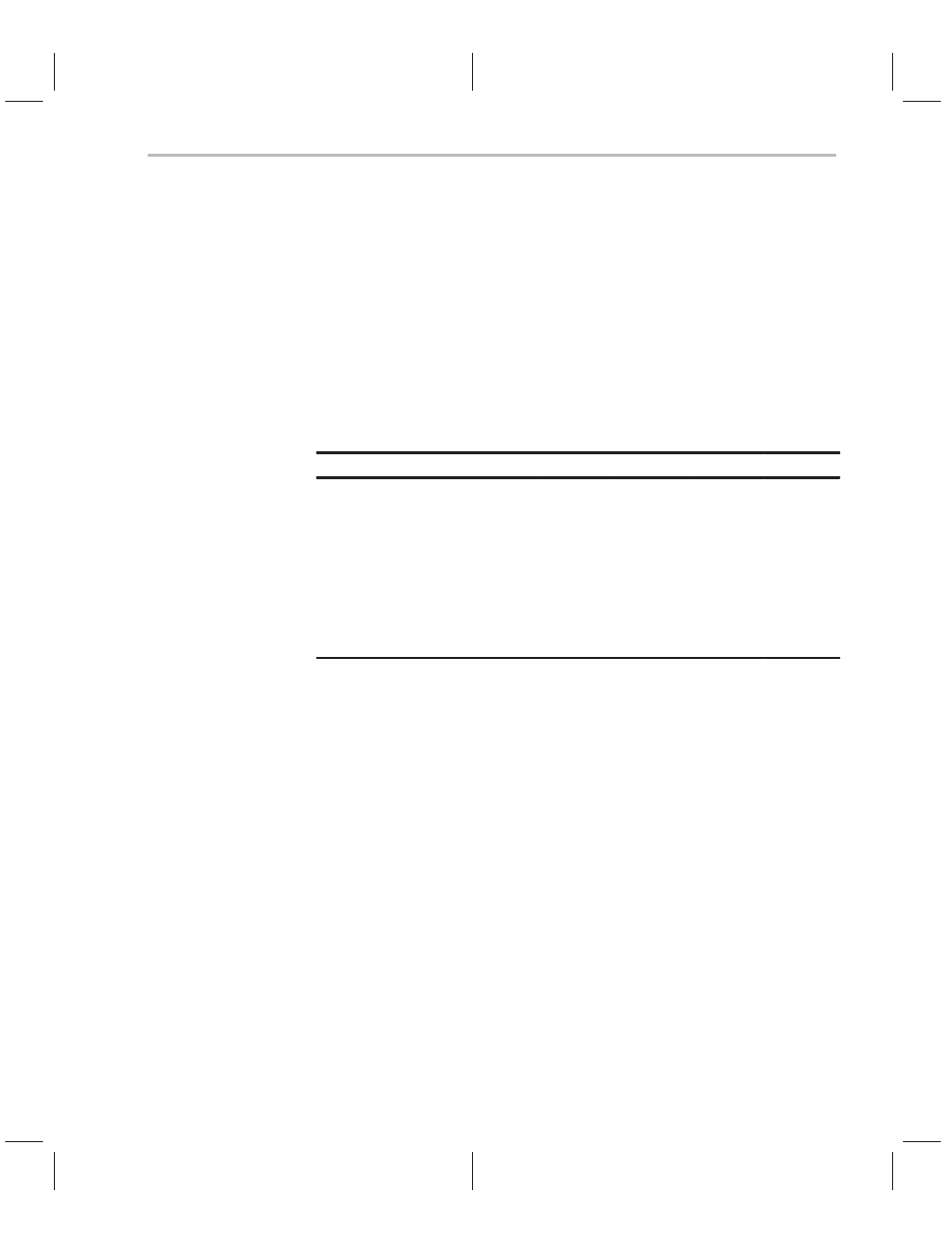

Table 2–1. Program and Data Memory on the TMS320C2xx Devices

Memory Type

’C203

’C204

’F206

’C209

ROM (words)

–

4K

–

4K

Flash memory (words)

–

–

32K

–

DARAM (words)

544

544

544

544

Data (words)

288

288

288

288

Data/program (words)

256

256

256

256

SARAM (words)

–

–

4K

4K

The ’C2xx also has CPU registers that are mapped in data memory space and

peripheral registers that are mapped in on-chip I/O space. The ’C2xx memory

types and features are introduced in the subsections following this paragraph.

For more details about the configuration and use of the ’C2xx memory and I/O

space, see Chapter 4,

Memory and I/O Space.

2.3.1

Dual-Access On-Chip RAM

All ’C2xx devices have 544 words

×

16-bits of on-chip DARAM, which can be

accessed twice per machine cycle. This memory is primarily intended to hold

data but, when needed, can also hold programs. It can be configured in one

of two ways:

-

All 544 words are configured as data memory.

-

288 words are configured as data memory, and 256 words are configured

as program memory.

Because DARAM can be accessed twice per cycle, it improves the speed of

the CPU. The CPU operates within a four-cycle pipeline. In this pipeline, the