Figure 7–4. lst #1 operation – Texas Instruments TMS320C2XX User Manual

Page 241

LST

Load Status Register

7-88

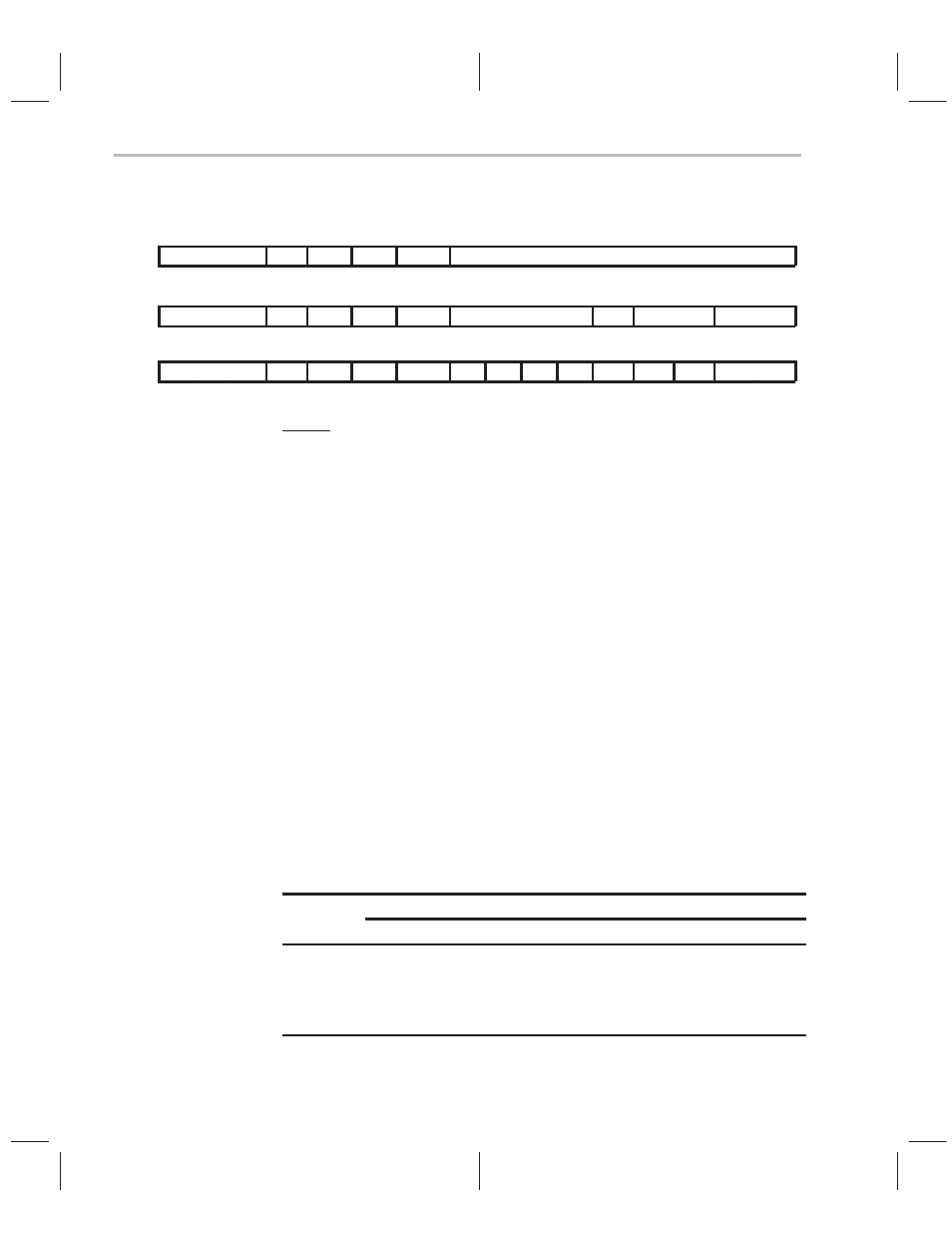

Figure 7–4. LST #1 Operation

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ST0

ARP

OV

OVM

1

INTM

DP

↑

↑

↑

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Data

↓

↓

↓

↓

↓

↓

↓

↓

↓

↓

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ST1

ARB

CNF

TC

SXM

C

1

1

1

1

XF

1

1

PM

Status Bits

Affects

ARB, ARP, OV, OVM, DP, CNF, TC, SXM, C, XF, and PM

This instruction does not affect INTM.

Description

The specified status register (ST0 or ST1) is loaded with the addressed data-

memory value. Note the following points:

-

The LST #0 operation does not affect the ARB field in the ST1 register,

even though a new ARP is loaded.

-

During the LST #1 operation, the value loaded into ARB is also loaded into

ARP.

-

If a next AR value is specified as an operand in the indirect addressing

mode, this operand is ignored. ARP is loaded with the three MSBs of the

value contained in the addressed data-memory location.

-

Reserved bit values in the status registers are always read as 1s. Writes

to these bits have no effect.

The LST instruction can be used for restoring the status registers after subrou-

tine calls and interrupts.

Words

1

Cycles for a Single LST Instruction

Program

Operand

ROM

DARAM

SARAM

External

DARAM

2

2

2

2+p

code

SARAM

2

2

2, 3

†

2+p

code

External

2+d

src

2+d

src

2+d

src

3+d

src

+p

code

† If the operand and the code are in the same SARAM block

Cycles