Texas Instruments TMS320C2XX User Manual

Page 366

Wait-State Generator

8-16

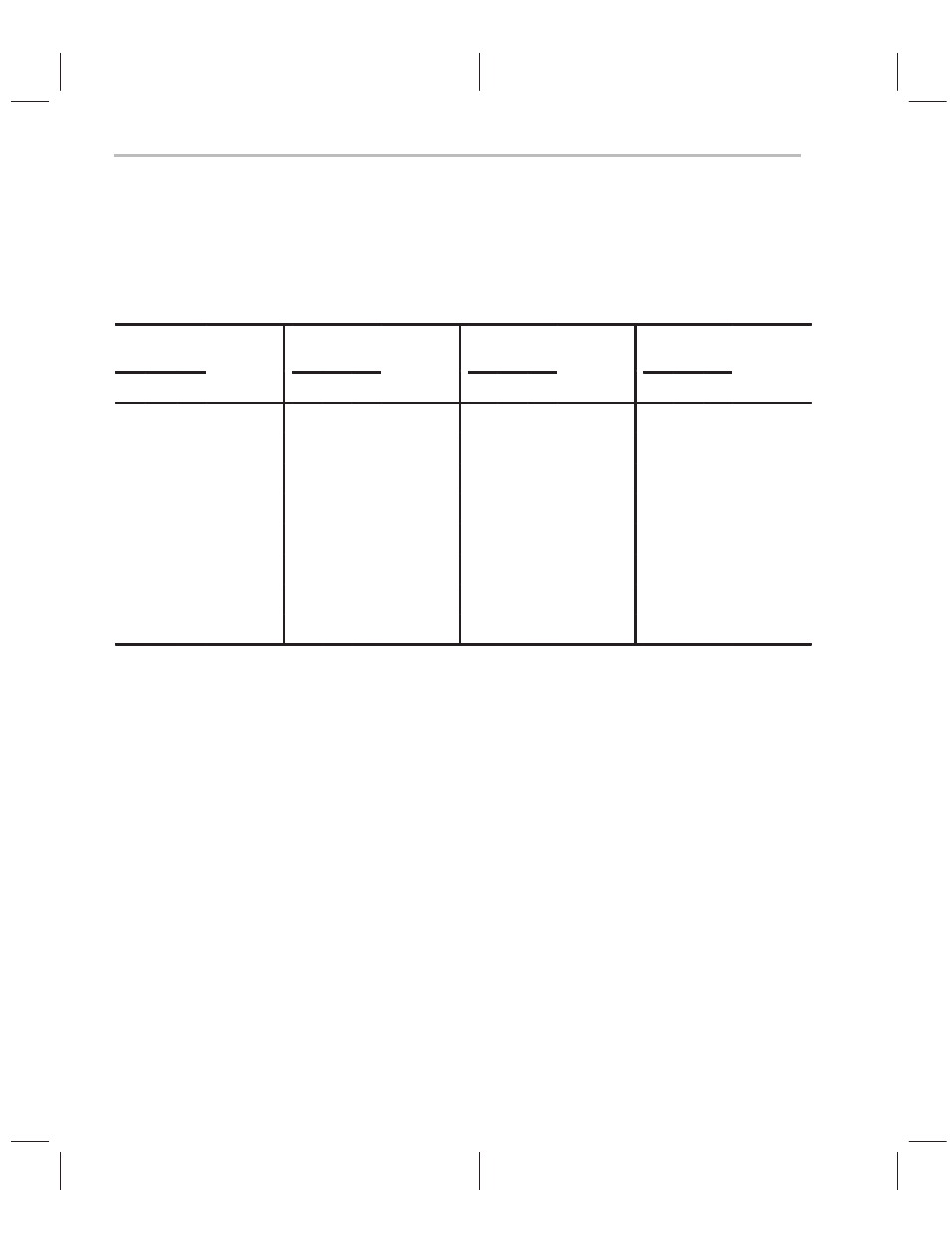

Table 8–4 shows how to set the number of wait states you want for each type

of off-chip memory. For example, if you write 1s to bits 0 through 5, the device

will generate seven wait states for off-chip lower program memory and seven

wait states for off-chip upper program memory.

Table 8–4. Setting the Number of Wait States With the ’C2xx WSGR Bits

ISWS Bits

I/O Wait

DSWS Bits

Data Wait

PSUWS

Bits

Upper

Program

Wait

PSLWS

Bits

Lower

Program

Wait

11

10

9

I/O Wait

States

8

7

6

Data Wait

States

5

4

3

Wait

States

2

1

0

Wait

States

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

2

0

1

0

2

0

1

0

2

0

1

0

2

0

1

1

3

0

1

1

3

0

1

1

3

0

1

1

3

1

0

0

4

1

0

0

4

1

0

0

4

1

0

0

4

1

0

1

5

1

0

1

5

1

0

1

5

1

0

1

5

1

1

0

6

1

1

0

6

1

1

0

6

1

1

0

6

1

1

1

7

1

1

1

7

1

1

1

7

1

1

1

7

In summary, the wait-state generator inserts zero to seven wait states to a giv-

en memory space, depending on the values of PSLWS, PSUWS, DSWS, and

ISWS, while the READY signal remains high. The READY signal may then be

driven low to generate additional wait states. If

m is the number of CLKOUT1

cycles required for a particular read or write operation and

w is the number of

wait states added, the operation will take (

m + w) cycles. At reset, all WSGR

bits are set to 1, making seven wait states the default for every memory space.