Texas Instruments TMS320C2XX User Manual

Page 187

AND

AND With Accumulator

7-34

Syntax

AND

dma

Direct addressing

AND

ind [, ARn]

Indirect addressing

AND #

lk [, shift]

Long immediate addressing

AND #

lk, 16

Long immediate with left

shift of 16

Operands

dma:

7 LSBs of the data-memory address

shift:

Left shift value from 0 to 15 (defaults to 0)

n:

Value from 0 to 7 designating the next auxiliary register

lk:

16-bit long immediate value

ind:

Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

AND

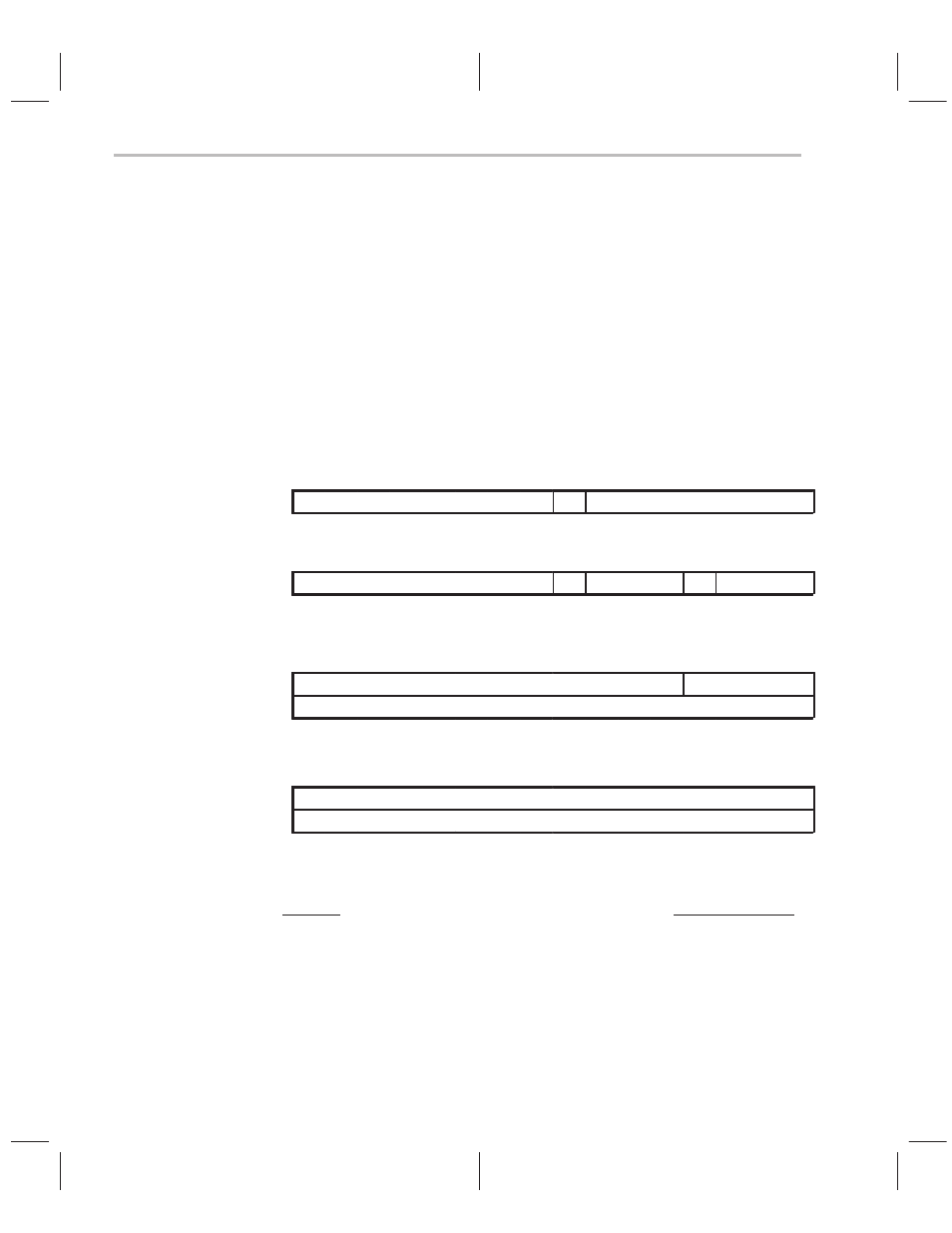

dma

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

1

1

0

1

1

1

0

0

dma

AND

ind [, ARn]

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

1

1

0

1

1

1

0

1

ARU

N

NAR

Note:

ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode (page 6-9).

AND #

lk [, shift]

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1

0

1

1

1

1

1

1

1

0

1

1

shift

lk

AND #

lk, 16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1

0

1

1

1

1

1

0

1

0

0

0

0

0

0

1

lk

Execution

Increment PC, then ...

Event(s)

Addressing mode

(ACC(15:0)) AND (data-memory address)

→

ACC(15:0) Direct or indirect

0

→

ACC(31:16)

(ACC(31:0)) AND lk

2

shift

→

ACC

Long immediate

(ACC(31:0)) AND lk

2

16

→

ACC

Long immediate

with left shift of 16

Opcode