Texas Instruments TMS320C2XX User Manual

Page 264

Modify Auxiliary Register

MAR

7-111

Assembly Language Instructions

Syntax

MAR

dma

Direct addressing

MAR

ind [, ARn]

Indirect addressing

Operands

n:

Value from 0 to 7 designating the next auxiliary register

ind:

Select one of the following seven options:

* *+ *– *0+ *0– *BR0+ *BR0–

MAR

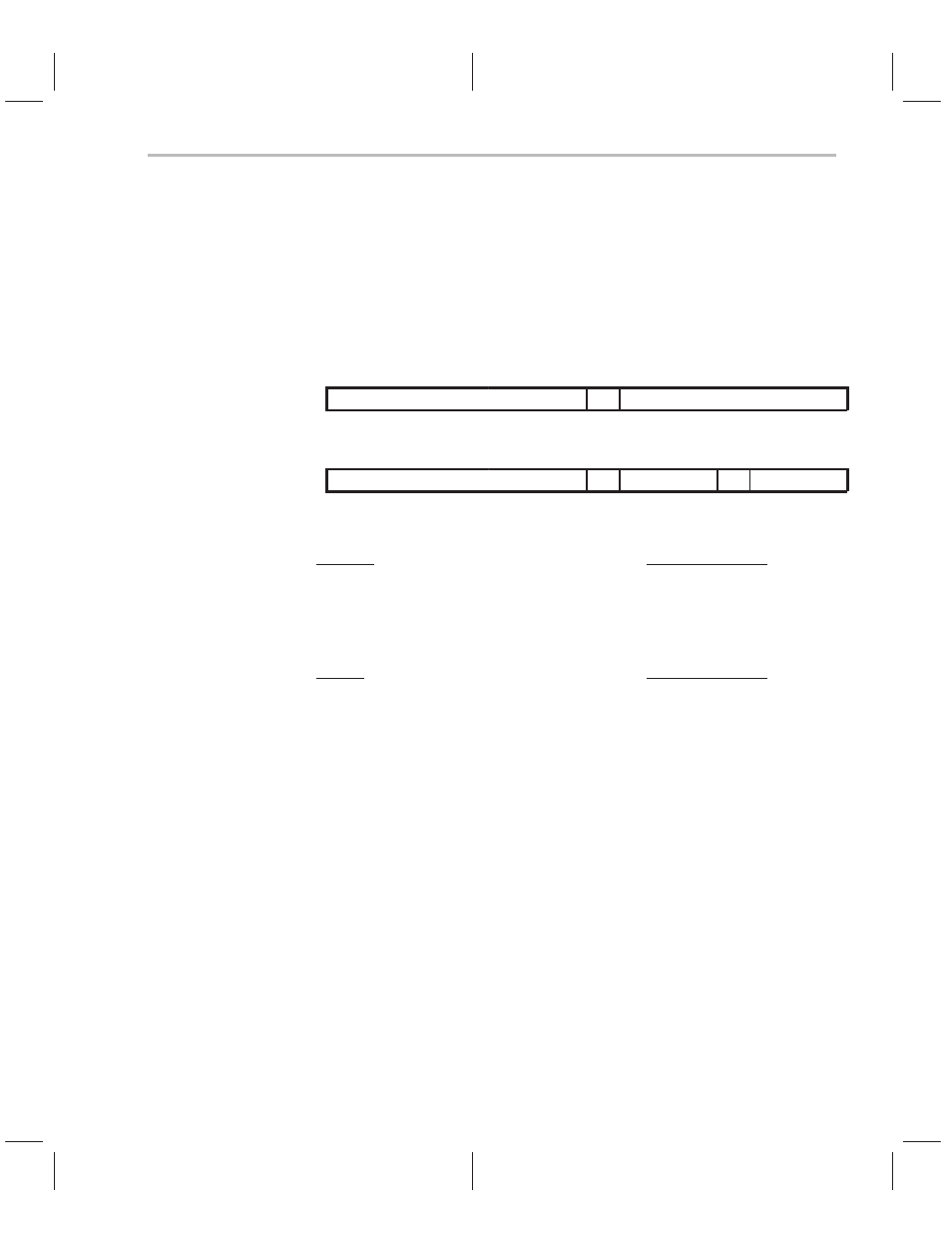

dma

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1

0

0

0

1

0

1

1

0

dma

MAR

ind [, ARn]

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1

0

0

0

1

0

1

1

1

ARU

N

NAR

Note:

ARU, N, and NAR are defined in Section 6.3,

Indirect Addressing Mode (page 6-9).

Execution

Event(s)

Addressing mode

Increment PC

Direct

Increment PC

Indirect

Modify (current AR) and (ARP) as specified

Status Bits

Affects

Addressing mode

None

Direct

ARP and ARB

Indirect

Description

In the direct addressing mode, the MAR instruction acts as a NOP instruction.

In the indirect addressing mode, an auxiliary register value and the ARP value

can be modified; however, the memory being referenced is not used. When

MAR modifies the ARP value, the old ARP value is copied to the ARB field of

ST1. Any operation that MAR performs with indirect addressing can also be

performed with any instruction that supports indirect addressing. In addition,

the ARP can also be loaded by an LST instruction.

The LARP instruction from the ’C25 instruction set is a subset of MAR. For ex-

ample, MAR *, AR4 performs the same function as LARP 4, which loads the

ARP with 4.

For loading an auxiliary register, see the description for the LAR instruction.

For storing an auxiliary register value to data memory, see the SAR instruction.

Opcode