Clrc – Texas Instruments TMS320C2XX User Manual

Page 215

CLRC

Clear Control Bit

7-62

Syntax

CLRC

control bit

Operands

control bit:

Select one of the following control bits:

C

Carry bit of status register ST1

CNF

RAM configuration control bit of status register ST1

INTM

Interrupt mode bit of status register ST0

OVM

Overflow mode bit of status register ST0

SXM

Sign-extension mode bit of status register ST1

TC

Test/control flag bit of status register ST1

XF

XF pin status bit of status register ST1

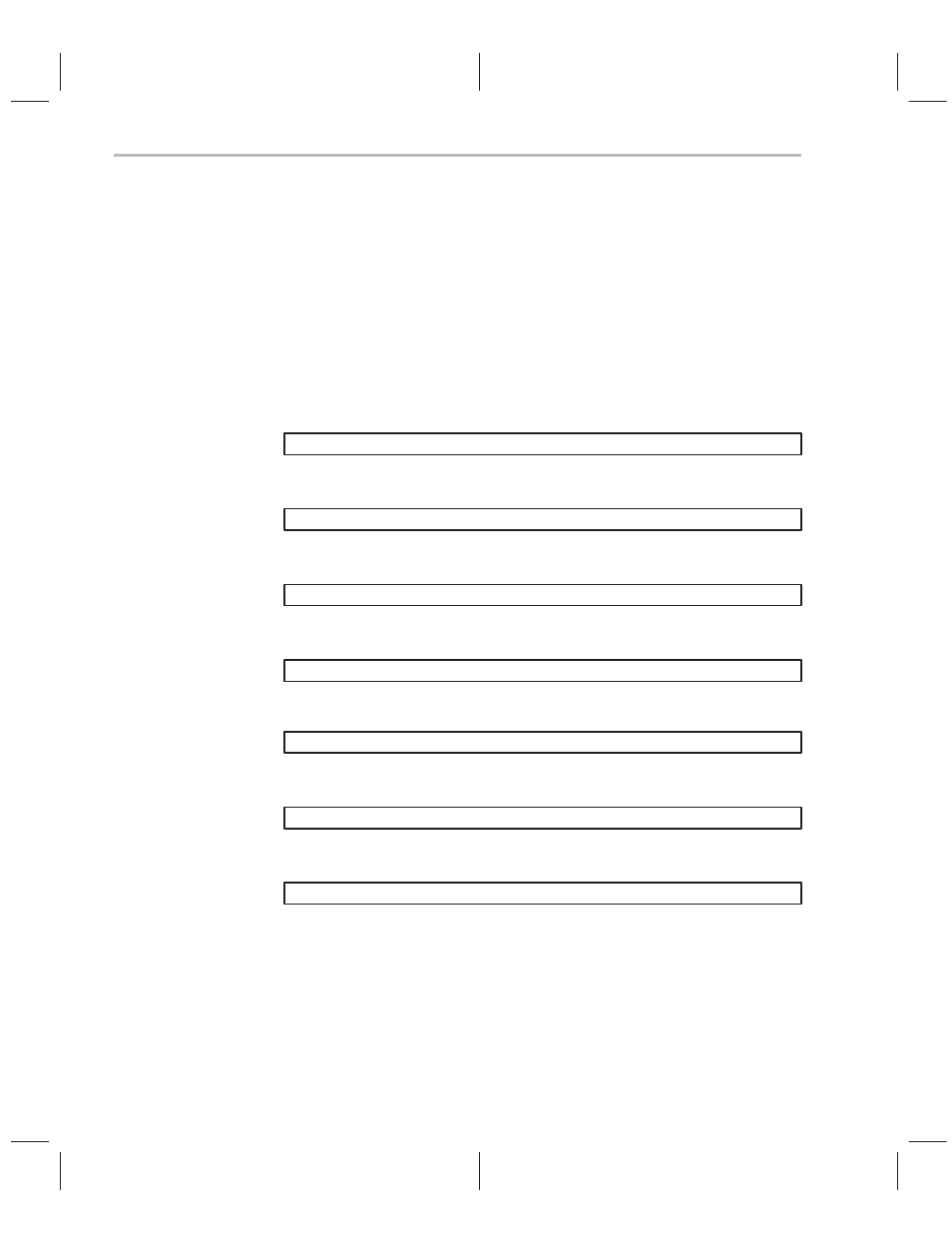

CLRC C

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

1

1

0

0

1

0

0

1

1

1

1

1

0

1

CLRC CNF

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

1

0

0

0

1

0

0

1

1

1

1

1

0

1

CLRC INTM

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

0

0

0

0

1

0

0

1

1

1

1

1

0

1

CLRC OVM

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

0

0

0

0

1

0

0

1

1

1

1

1

0

1

CLRC SXM

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

1

0

0

0

1

0

0

1

1

1

1

1

0

1

CLRC TC

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

0

1

0

0

1

0

0

1

1

1

1

1

0

1

CLRC XF

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

0

1

1

0

0

1

0

0

1

1

1

1

1

0

1

Execution

Increment PC, then ...

0

→

control bit

Status Bits

None

Description

The specified control bit is cleared to 0. Note that the LST instruction can also

be used to load ST0 and ST1. See subsection 3.5,

Status Registers ST0 and

ST1 on page 3-15, for more information on each of these control bits.

Opcode