Texas Instruments TMS320C2XX User Manual

Page 326

Store Status Register

SST

7-173

Assembly Language Instructions

Status registers ST0 and ST1 are defined in Section 3.5,

Status Registers ST0

and ST1, on page 3-15.

Words

1

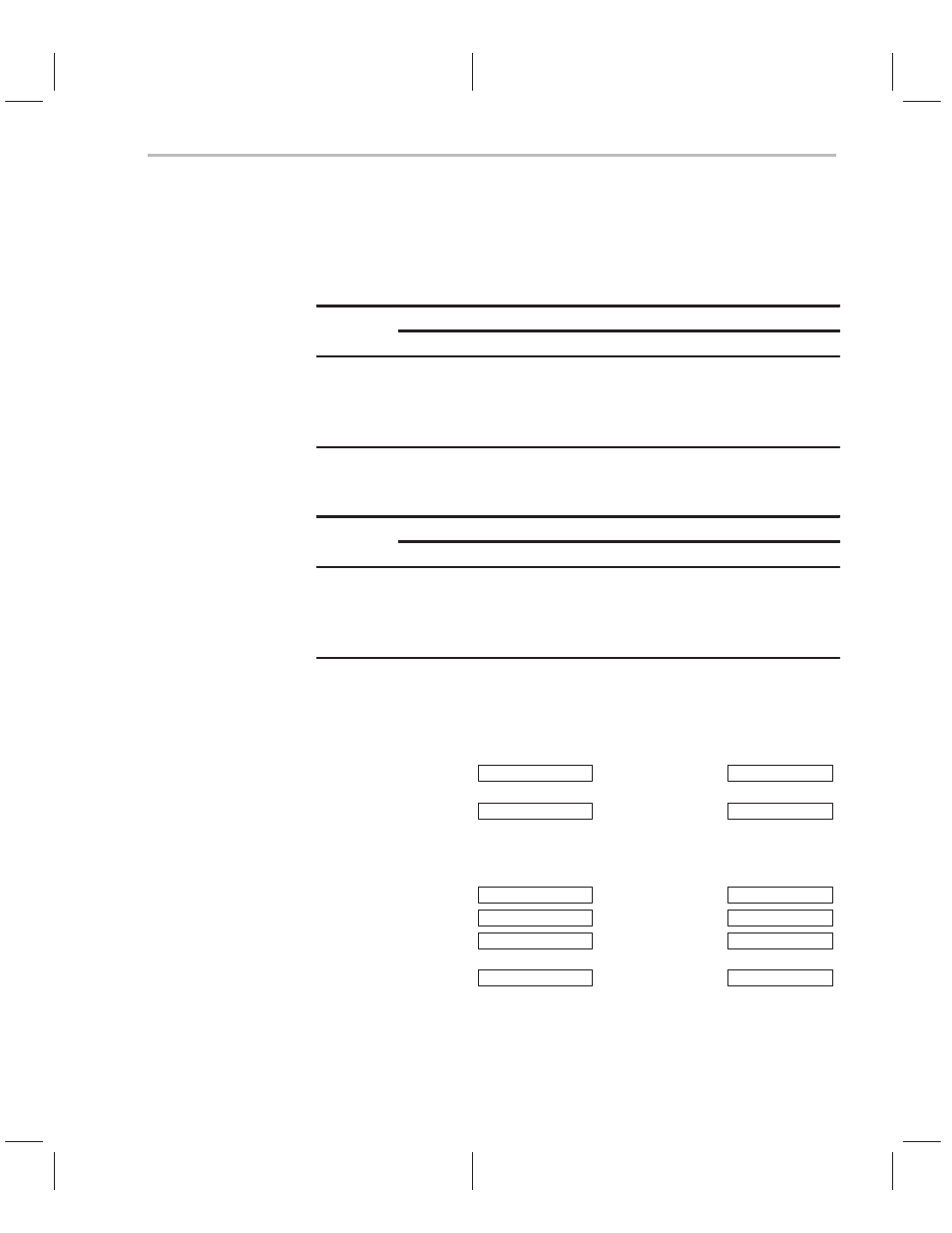

Cycles for a Single SST Instruction

Program

Operand

ROM

DARAM

SARAM

External

DARAM

1

1

1

1+p

SARAM

1

1

1, 2

†

1+p

External

2+d

2+d

2+d

4+d+p

† If the operand and the code are in the same SARAM block

Cycles for a Repeat (RPT) Execution of an SST Instruction

Program

Operand

ROM

DARAM

SARAM

External

DARAM

n

n

n

n+p

SARAM

n

n

n, n+2

†

n+p

External

2n+nd

2n+nd

2n+nd

2n+2+nd+p

† If the operand and the code are in the same SARAM block

Example 1

SST

#0,96

(Direct addressing: data page 0

;accessed automatically)

Before Instruction

After Instruction

ST0

0A408h

ST0

0A408h

Data Memory

Data Memory

60h

0Ah

60h

0A408h

Example 2

SST

#1,*,AR7

(Indirect addressing)

Before Instruction

After Instruction

ARP

0

ARP

7

AR0

300h

AR0

300h

ST1

2580h

ST1

2580h

Data Memory

Data Memory

300h

0h

300h

2580h

Cycles