Program counter (pc) – Texas Instruments TMS320C2XX User Manual

Page 102

Program-Address Generation

5-3

Program Control

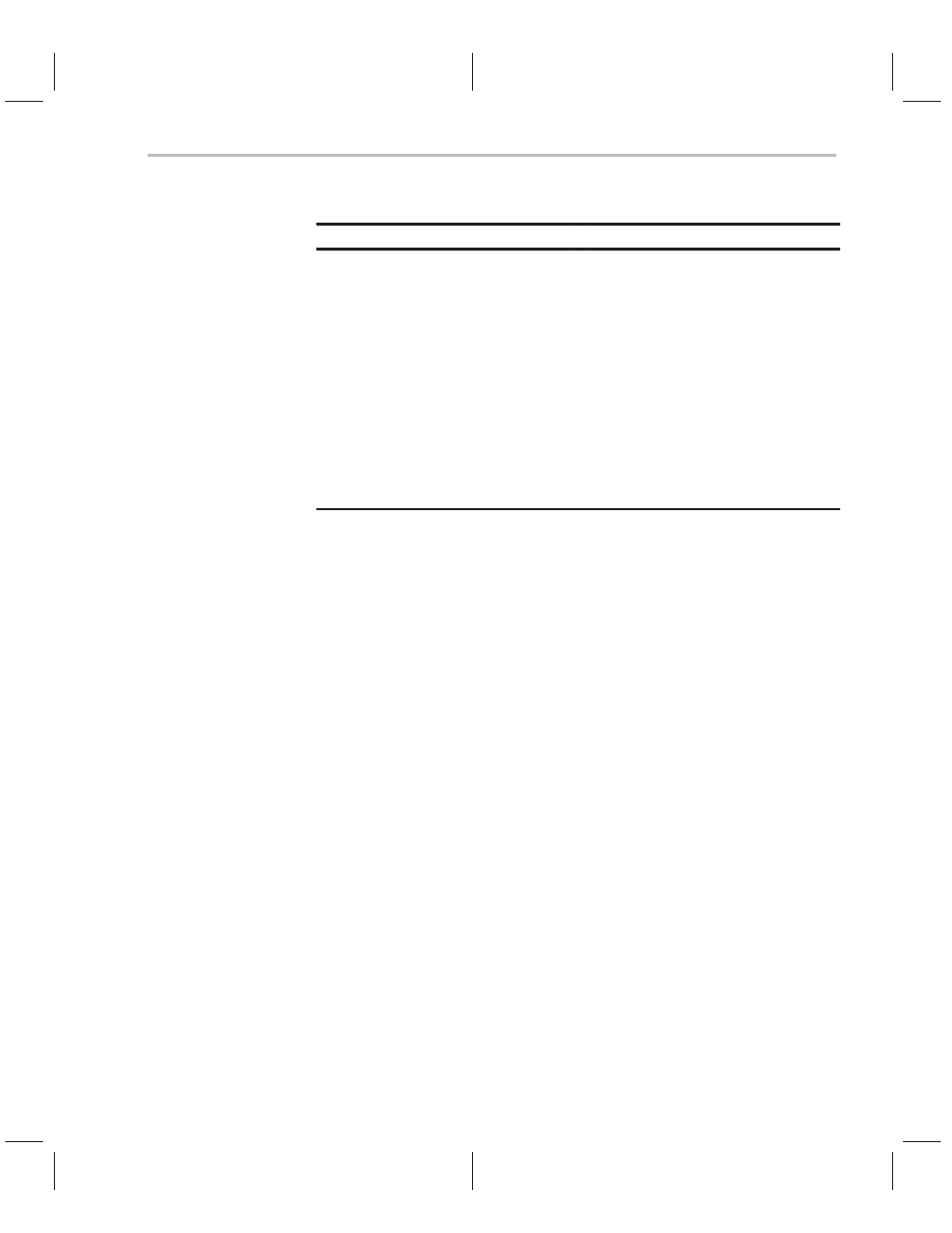

Table 5–1. Program-Address Generation Summary

БББББББББББ

БББББББББББ

Operation

ББ

ББ

ББББББББББББ

ББББББББББББ

Program-Address Source

БББББББББББ

БББББББББББ

Sequential operation

ББ

ББ

ББББББББББББ

ББББББББББББ

PC (contains program address +1)

БББББББББББ

БББББББББББ

Dummy cycle

ББ

ББ

ББББББББББББ

ББББББББББББ

PAR (contains program address)

БББББББББББ

Б

БББББББББ

Б

БББББББББББ

Return from subroutine

ББ

ББ

ББ

ББББББББББББ

Б

ББББББББББ

Б

ББББББББББББ

Top of the stack (TOS)

БББББББББББ

БББББББББББ

Return from table move or block move

ББ

ББ

ББББББББББББ

ББББББББББББ

Micro stack (MSTACK)

БББББББББББ

Б

БББББББББ

Б

БББББББББББ

Branch or call to address specified in

instruction

ББ

ББ

ББ

ББББББББББББ

Б

ББББББББББ

Б

ББББББББББББ

Branch or call instruction by way of the

program read bus (PRDB)

БББББББББББ

Б

БББББББББ

Б

БББББББББББ

Branch or call to address specified in

lower half of the accumulator

ББ

ББ

ББ

ББББББББББББ

Б

ББББББББББ

Б

ББББББББББББ

Low accumulator by way of the data

read bus (DRDB)

БББББББББББ

Б

БББББББББ

Б

БББББББББББ

Branch to interrupt service routine

ББ

ББ

ББ

ББББББББББББ

Б

ББББББББББ

Б

ББББББББББББ

Interrupt vector location by way of the

program read bus (PRDB)

The ’C2xx program-address generation logic uses the following hardware:

-

Program counter (PC). The ’C2xx has a 16-bit program counter (PC) that

addresses internal and external program memory when fetching instruc-

tions.

-

Program address register (PAR). The PAR drives the program address

bus (PAB). The PAB is a 16-bit bus that provides program addresses for

both reads and writes.

-

Stack. The program-address generation logic includes a 16-bit-wide, 8-

level hardware stack for storing up to eight return addresses. In addition,

you can use the stack for temporary storage.

-

Micro stack (MSTACK). Occasionally, the program-address generation

logic uses the 16-bit-wide, 1-level MSTACK to store one return address.

-

Repeat counter (RPTC). The 16-bit RPTC is used with the repeat (RPT)

instruction to determine how many times the instruction following RPT is

repeated.

5.1.1

Program Counter (PC)

The program-address generation logic uses the 16-bit program counter (PC)

to address internal and external program memory. The PC holds the address

of the next instruction to be executed. Through the program address bus

(PAB), an instruction is fetched from that address in program memory and

loaded into the instruction register. When the instruction register is loaded, the

PC holds the next address.