4 telecom status/control register, 5 interrupt mask and map registers, Table 6-61 – Artesyn ATCA-7365 Installation and Use (November 2014) User Manual

Page 212: Telecom status/control register, Table 6-62, Address map of interrupt mask and map registers, Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65N)

212

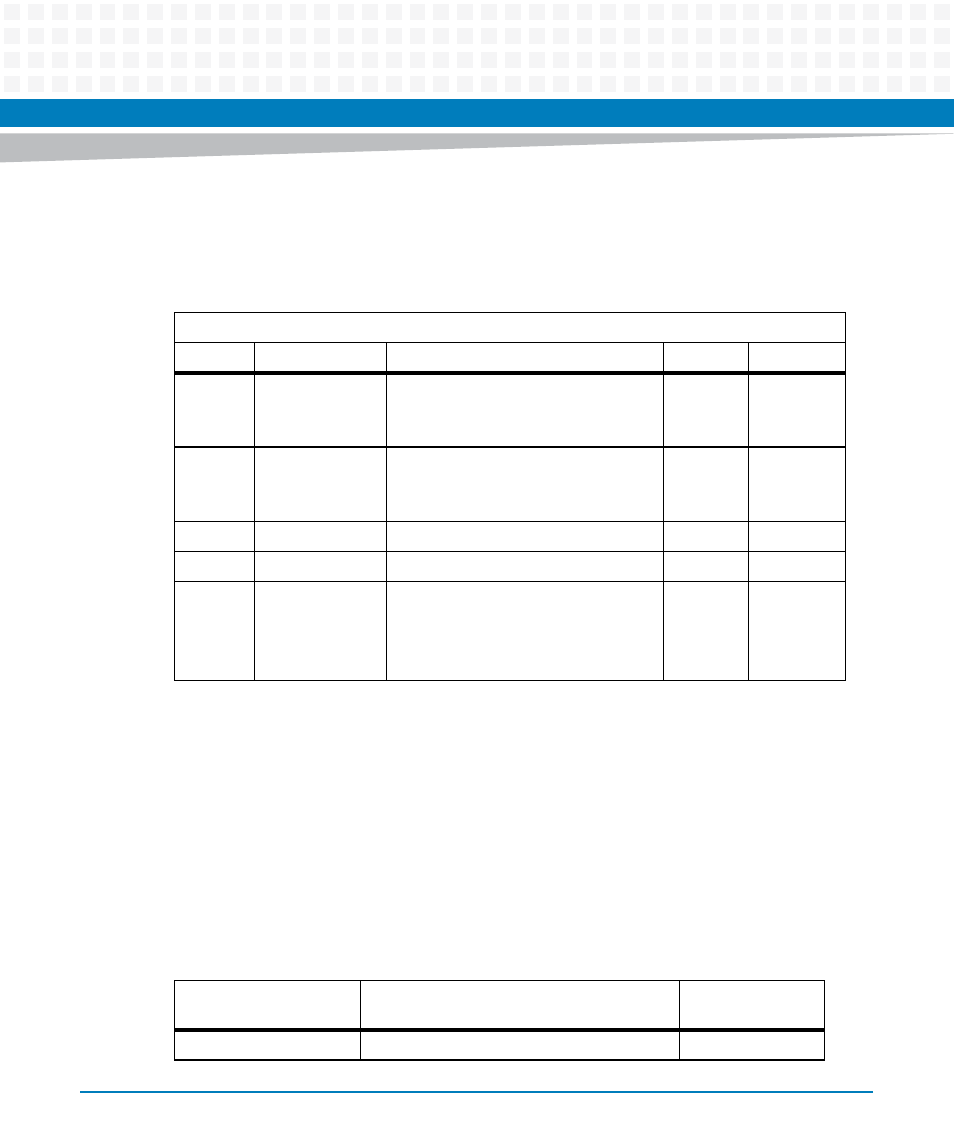

6.4.12.4 Telecom Status/Control Register

The following table provides a detailed description about Telecom Status/Control Register.

6.4.12.5 Interrupt Mask and Map Registers

Each interrupt signal of the External Interrupt Status Register, Processor Hot Status/Control

Register or Telecom Status/Control Register can be mapped to one of the CPU_IRQ_X_

interrupt or any IRQ Frame number of the serialized IRQ protocol.

Multiple interrupt sources may share the same CPU_IRQ_X_ or the same IRQ Frame. In this

case all interrupt sources need to be of type “level active low”.

Each Interrupt source has an Interrupt Mask and Map Register, mentioned in the table below.

Table 6-61 Telecom Status/Control Register

Address Offset: 0x22

Bit

Signal

Description

Default

Access

0

CH1_CLK1A_IN

Clock CLK1A of Chassis 1 has changed

state from static to toggle or toggle to

static.

0

LPC: r/w1c

1

CH1_CLK1B_IN

Clock CLK1A of Chassis 1 has changed

state from static to toggle or toggle to

static.

0

LPC: r/w1c

2

-

Telecom timeout occurred.

0

LPC: r/w1c

3

-

Reserved

-

r

7:4

-

Counter of Telecom timeout occurred.

Clearing bit 2 of this register also clears

this

counter.

0

LPC: r

Table 6-62 Address Map of Interrupt Mask and Map Registers

Interrupt Source

Description

Address Offset of

Interrupt Mask

IPMC2HOST_INT_

IPMC signals interrupt

0x23