3 programmable baud rate generator, Table 6-38, Divisor latch lsb register (dll), if dlab=1 – Artesyn ATCA-7365 Installation and Use (November 2014) User Manual

Page 195: Table 6-39, Divisor latch msb register (dlm), if dlab=1, Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65N)

195

6.3.4.3

Programmable Baud Rate Generator

The UART contains a programmable Baud Rate Generator that is capable of taking the

UART_CLK input and dividing it by any divisor from 1 to 65535 (2

16

-1). The output frequency

of the Baud Rate Generator is 16 times the baud rate. Two 8-bit latches store the divisor in a 16-

bit binary format. These Divisor Latches must be loaded during initialization to ensure proper

operation of the Baud Rate Generator. If both Divisor Latches are loaded with 0, the 16X output

clock is stopped. Upon loading either of the Divisor latches, a 16-bit baud counter is

immediately loaded. This prevents long counts on initial load. Access to the Divisor latch can be

done with a word write.

The UART_CLK is the CLK_UART (48MHz) input divided by the pre-divider set by the Super IO

Configuration Register (Offset 0x29).

The baud rate of the data shifted in/out of the UART is given by:

Baud Rate = UART_CLK / (16X Divisor)

For example, if the pre-divider is 26 the UART_CLK is 1.8461538MHz. When the divisor is 12,

the baud rate is 9600.

A Divisor value of 0 in the Divisor Latch Register is not allowed.

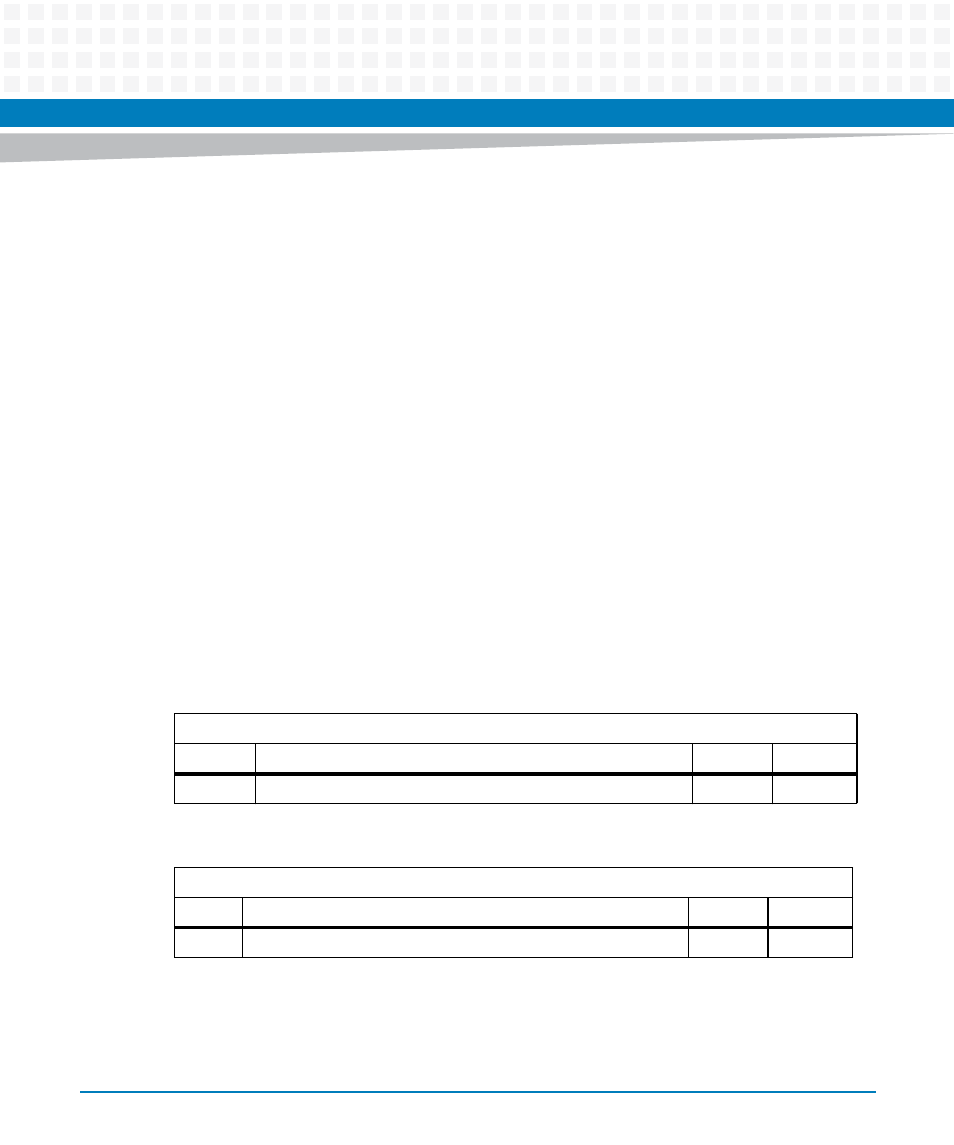

Table 6-38 Divisor Latch LSB Register (DLL), if DLAB=1

LPC IO Address: Base

Bit

Description

Default

Access

7:0

Divisor Latch LSB (DLL)

Undef.

LPC: r/w

Table 6-39 Divisor Latch MSB Register (DLM), if DLAB=1

LPC IO Address: Base + 1

Bit

Description

Default

Access

7:0

Divisor Latch MSB (DLM)

Undef.

LPC: r/w