Table 6-16, Table 6-17, Logical device configuration register summary – Artesyn ATCA-7365 Installation and Use (November 2014) User Manual

Page 176: Maps and registers, 2 logical device configuration registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65N)

176

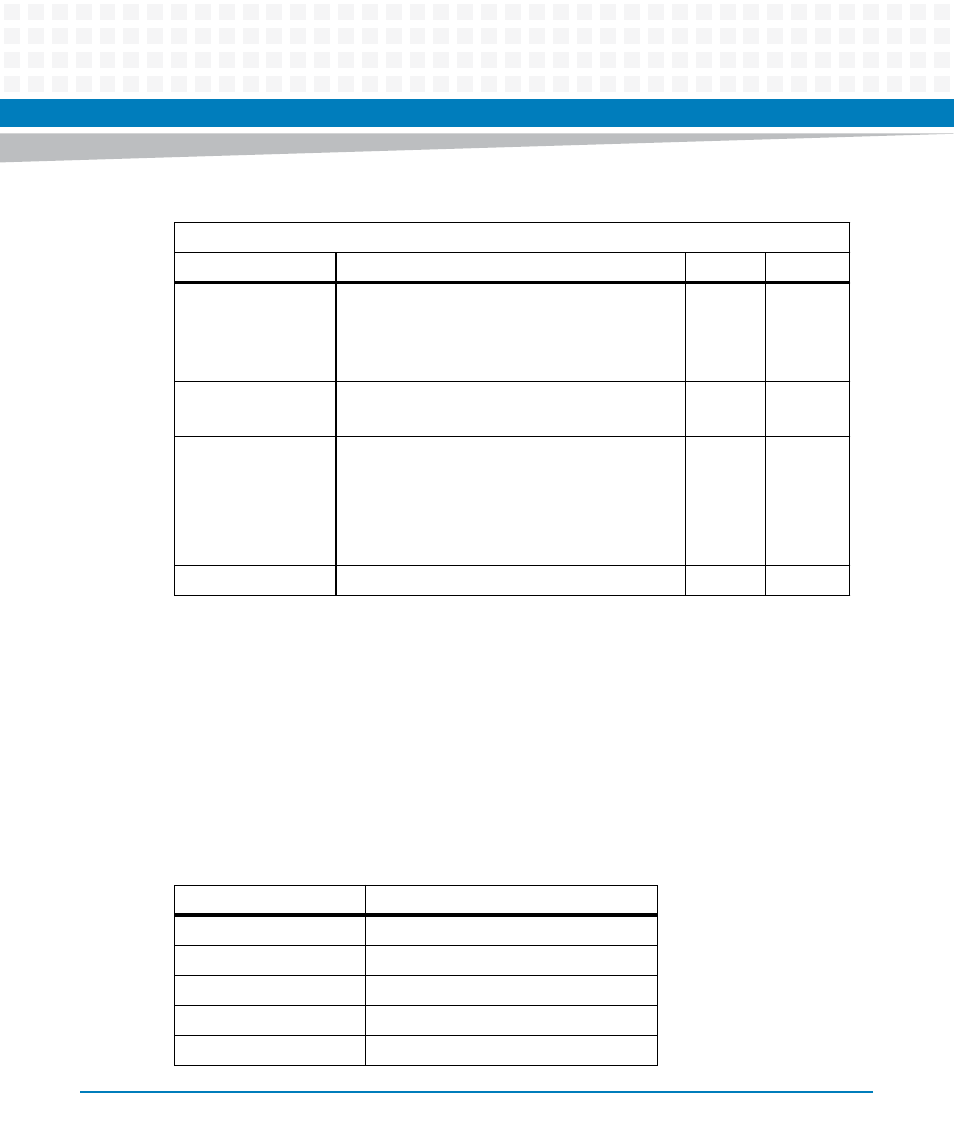

6.3.3.3.2 Logical Device Configuration Registers

These registers are used to access the registers that are assigned to each logical unit. The Super

IO supports two logical units and has two sets of logical device registers. The two logical

devices are UART1 (Logical Number 4) and UART2 (Logical Number 5). A separate set (bank) of

control and configuration registers exists for each logical device and is selected with the

Logical Device Number Register. The INDEX PORT is used to select a specific logical device

register. These registers are then accessed through the DATA PORT. The Logical Device

registers are accessible only when the device is in the Configuration state.

Table 6-16 Global Super IO SERIRQ and Pre-divide Control Register

Index Address: 0x29

Bit

Description

Default

Access

0

SERIRQ enable:

0: disabled. Serial interrupts disabled.

1: enabled. Logical devices participate in interrupt

generations.

0

LPC: r/w

1

SERIRQ Mode:

1: Continuous Mode

1

LPC: r

3:2

UART Clock pre-divide

00: divide by 1

01: divide by 8

10: divide by 26 (CLK_UART is 48 MHz)

11: reserved

0

LPC: r/w

7:4

Reserved

0

LPC: r

Table 6-17 Logical Device Configuration Register Summary

Index Address

Description

0x30 Enable

0x60

Base IO Address MSB

0x61

Base IO Address LSB

0x70

Primary Interrupt Select

0x74

Reserved