11 rtm spi interface registers, Table 6-56, Rtm spi address/command register – Artesyn ATCA-7365 Installation and Use (November 2014) User Manual

Page 209: Table 6-57, Rtm spi write register, Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65N)

209

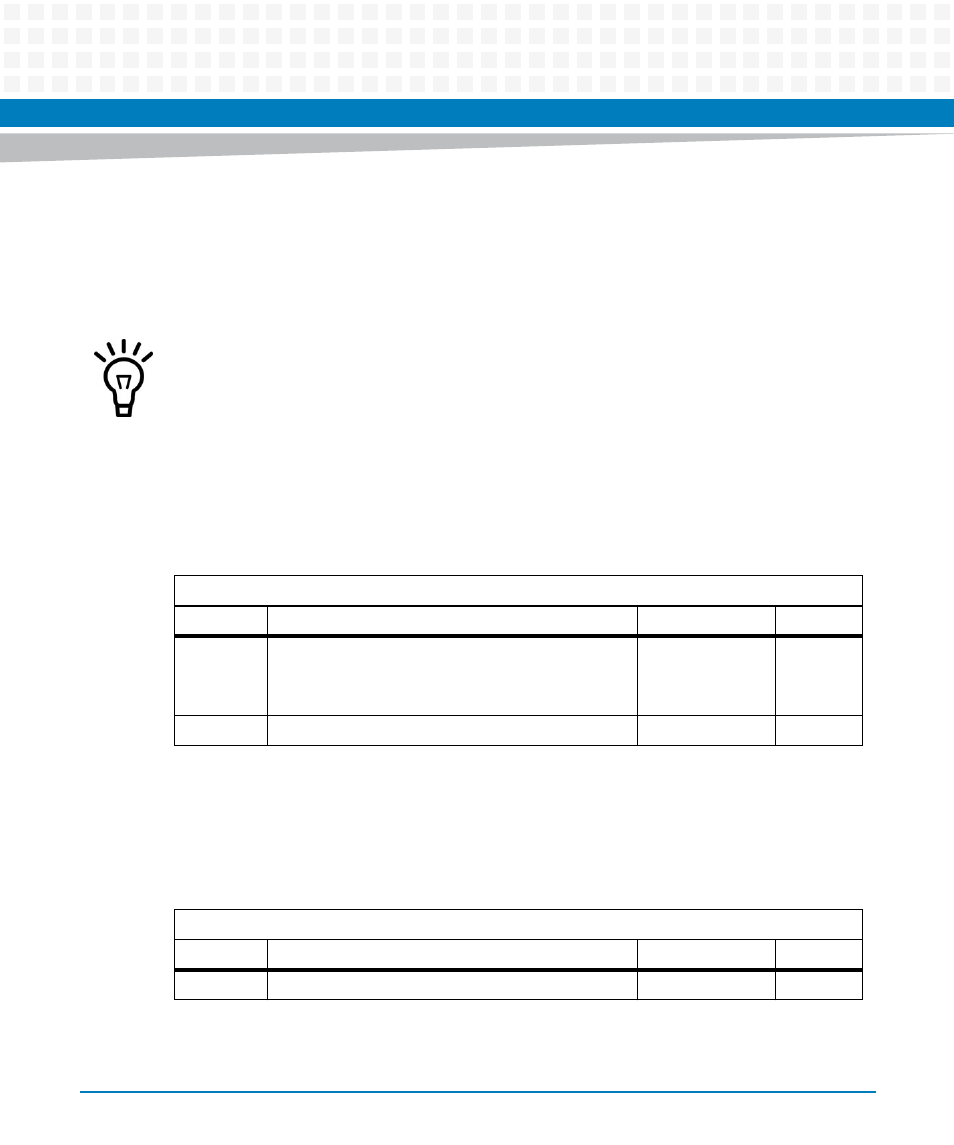

6.4.11 RTM SPI Interface Registers

The signals RTM_SPI_SCK, RTM_SPI_SS_, RTM_SPI_MISO and RTM_SPI_MOSI are used to

support a SPI master protocol. The signal RTM_SPI_MISO is used to signal the base board an

ARTM interrupt.

A write access to the RTM SPI Address/Command Register starts the SPI transaction. The write

access terminates, when SPI transaction has finished.

A write access to the RTM SPI Address/Command Register with the Command Bit 0 (Write)

starts a SPI write transaction. The value of the RTM SPI Write Register is written to the SPI

device.

At the moment there is no ARTM with an SPI interface defined.

Table 6-56 RTM SPI Address/Command Register

Address Offset: 0x18

Bit

Description

Default

Access

0

Command Bit

0: Write

1: Read

0

IPMC: r/w

7:1

RTM SPI Address bits [6:0]

PWR_GOOD:0

IPMC: r/w

Table 6-57 RTM SPI Write Register

Address Offset: 0x19

Bit

Description

Default

Access

7:0

RTM SPI write data

-

LPC: w