1 uart register overview, Table 6-26, Uart register overview – Artesyn ATCA-7365 Installation and Use (November 2014) User Manual

Page 180: Maps and registers

Maps and Registers

ATCA-7365 Installation and Use (6806800K65N)

180

6.3.4.1

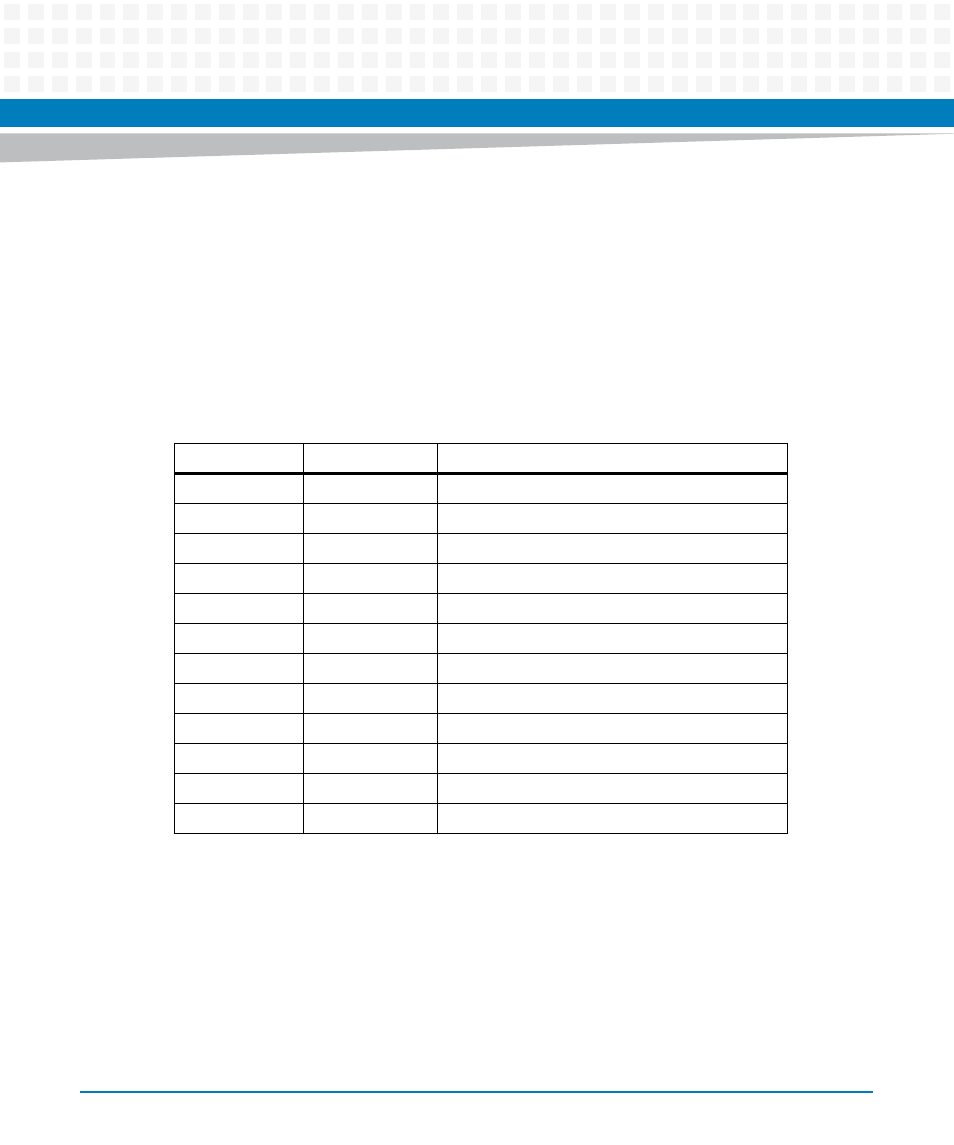

UART Register Overview

shows the registers and their addresses as offsets of a base address for

one of the two UARTs.

The state of the Divisor Latch Bit (DLAB), which is the MOST significant bit of the Serial Line

Control Register (SCR), affects the selection of certain of the UART registers. The DLAB bit must

be set high by the system software to access the Baud Rate Generator Divisor Latches (DLL and

DLM).

Table 6-26 UART Register Overview

LPC IO Address

DLAB Bit value

Description

Base

0

Receiver Buffer (RBR). Read Only

Base

0

Transmitter Holding (THR). Write Only.

Base + 1

0

Interrupt Enable Register (IER)

Base + 2

X

Interrupt Identification Register (IIR). Read Only

Base + 2

X

FIFO Control Register (FCR). Write Only.

Base + 3

X

Line Control Register (LCR)

Base + 4

X

Modem Control Register (MCR)

Base + 5

X

Line Status Register (LSR). Read Only

Base + 6

X

Modem Status Register (MSR). Read Only

Base + 7

X

Scratch Pad Register (SCR)

Base

1

Divisor Latch LSB (DLL)

Base + 1

1

Divisor Latch MSB (DLM)