Maxim Integrated 71M6513H Power Meter IC Family Software User Manual

Page 130

71M651x Software User’s Guide

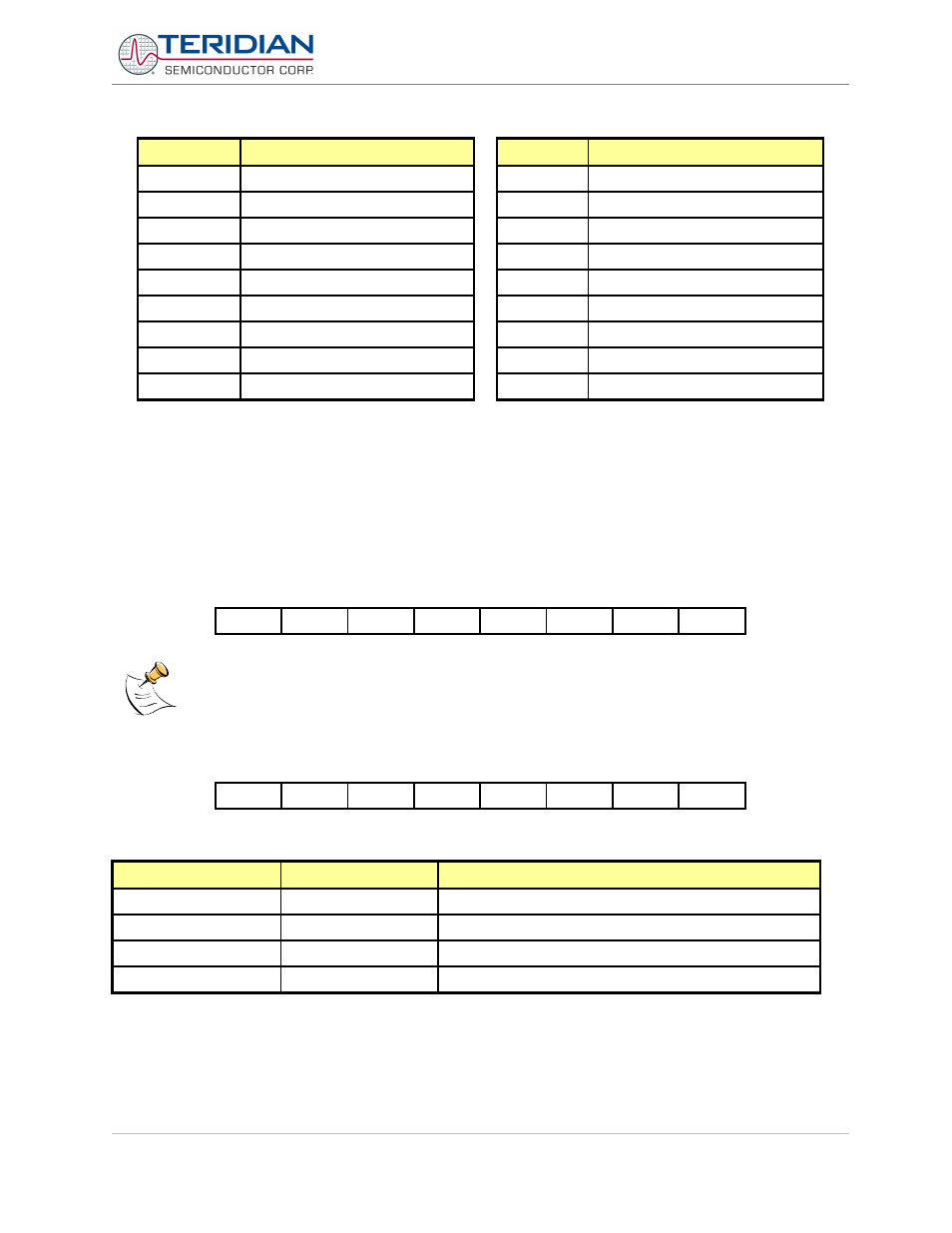

Enable Bit

Description

Flag Bit

Description

EX0

Enable external interrupt 0

IE0

External interrupt 0 flag

EX1

Enable external interrupt 1

IE1

External interrupt 1 flag

EX2

Enable external interrupt 2

IEX2

External interrupt 2 flag

EX3

Enable external interrupt 3

IEX3

External interrupt 3 flag

EX4

Enable external interrupt 4

IEX4

External interrupt 4 flag

EX5

Enable external interrupt 5

IEX5

External interrupt 5 flag

EX6

Enable external interrupt 6

IEX6

External interrupt 6 flag

EX_XFER

Enable XFER_BUSY interrupt

IE_XFER

XFER_BUSY interrupt flag

EX_RTC

Enable RTC_1SEC interrupt

IE_RTC

RTC_1SEC interrupt flag

Table 6-53: Control Bits for External Interrupts

SFR (special function register) enable bits must be set to permit any of these interrupts to occur. Likewise, each

interrupt has its own flag bit which is set by the interrupt hardware and is reset automatically by the MPU interrupt

handler (0 through 5). XFER_BUSY and RTC_1SEC, which are OR-ed together, have their own enable and flag bits in

addition to the interrupt 6 enable and flag bits (see Table 6-52), and these interrupts must be cleared by the MPU

software.

Interrupt Priority 0 Register (IP0)

MSB

LSB

owds

Wdts

IP0.5

IP0.4

IP0.3

IP0.2

IP0.1

IP0.0

Table 6-54: The IP0 Register:

owds, wdts are not used for interrupt controls

Interrupt Priority 1 Register (IP1)

MSB

LSB

-

-

IP1.5

IP1.4

IP1.3

IP1.2

IP1.1

IP1.0

Table 6-55: The IP1 Register:

IP1.x

IP0.x

Priority Level

0

0

Level0 (lowest)

0

1

Level1

1

0

Level2

1

1

Level3 (highest)

Table 6-56: Priority Levels

Revision 2.4

TERIDIAN Proprietary

130 of 137

© Copyright 2005-2006 TERIDIAN Semiconductor Corporation