3 adcsrb – adc control and status register b – Rainbow Electronics ATtiny10 User Manual

Page 94

94

8127B–AVR–08/09

ATtiny4/5/9/10

• Bit 4 – ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the data registers are updated. The ADC

Conversion Complete Interrupt is requested if the ADIE bit is set. ADIF is cleared by hardware

when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by

writing a logical one to the flag.

• Bit 3 – ADIE: ADC Interrupt Enable

When this bit is written to one, the ADC Conversion Complete Interrupt request is enabled.

• Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

These bits determine the division factor between the system clock frequency and the input clock

to the ADC.

13.12.3

ADCSRB

–

ADC Control and Status Register B

• Bits 7:3 – Res: Reserved Bits

These bits are reserved and will always read zero.

• Bits 2:0 – ADTS2:0: ADC Auto Trigger Source

If ADATE in ADCSRA is written to one, the value of these bits selects which source will trigger

an ADC conversion. If ADATE is cleared, the ADTS2:0 settings will have no effect. A conversion

will be triggered by the rising edge of the selected Interrupt Flag. Note that switching from a trig-

ger source that is cleared to a trigger source that is set, will generate a positive edge on the

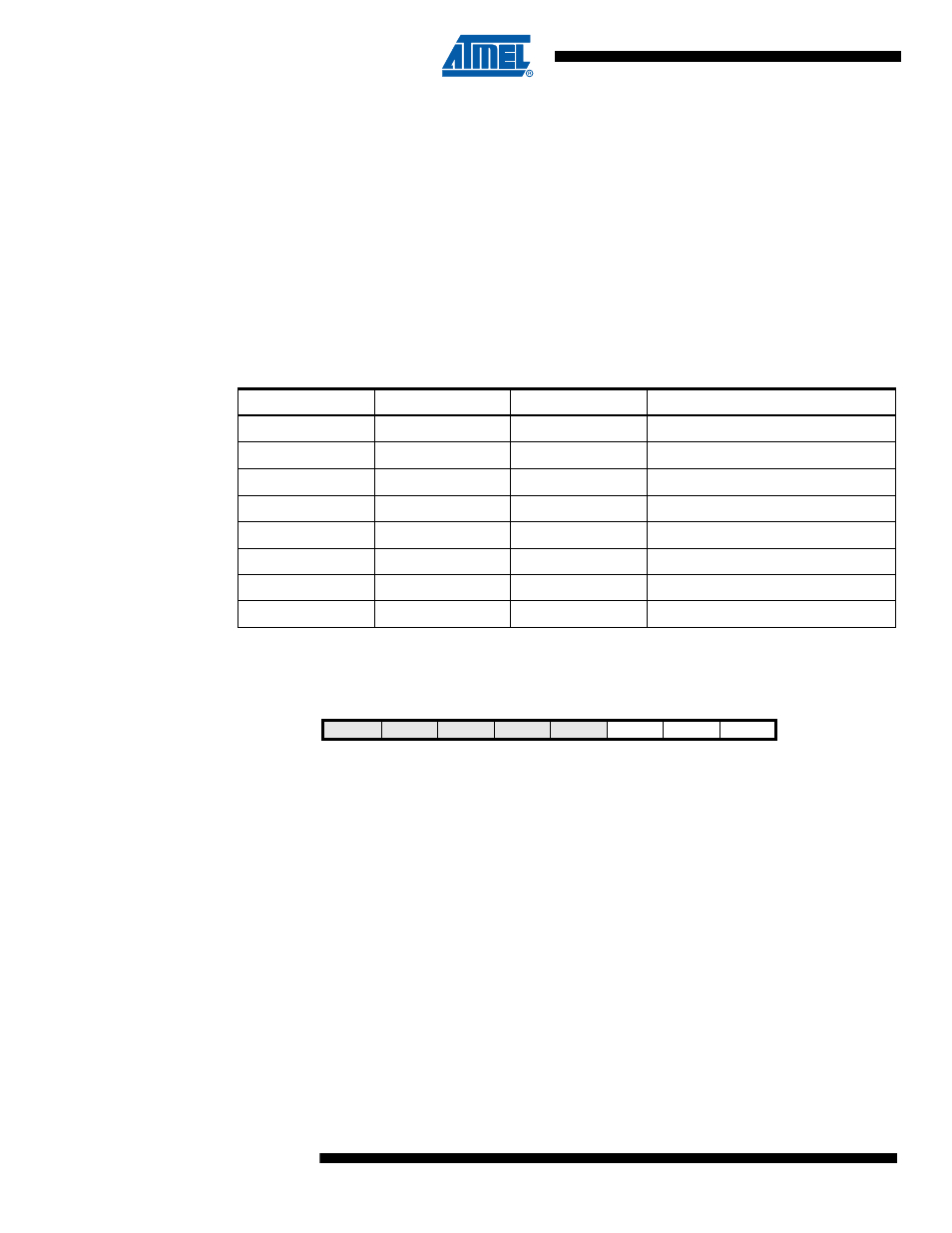

Table 13-3.

ADC Prescaler Selections

ADPS2

ADPS1

ADPS0

Division Factor

0

0

0

2

0

0

1

2

0

1

0

4

0

1

1

8

1

0

0

16

1

0

1

32

1

1

0

64

1

1

1

128

Bit

7

6

5

4

3

2

1

0

0x1C

–

–

–

–

–

ADTS2

ADTS1

ADTS0

ADCSRB

Read/Write

R

R

R

R

R

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0