3 external reset, 4 watchdog reset – Rainbow Electronics ATtiny10 User Manual

Page 29

29

8127B–AVR–08/09

ATtiny4/5/9/10

The VLM can also be used to improve reset characteristics at falling supply. Without VLM, the

Power-On Reset (POR) does not activate before supply voltage has dropped to a level where

the MCU is not necessarily functional any more. With VLM, it is possible to generate a reset at

supply voltages where the MCU is still functional.

When active, the VLM circuit consumes some power, as illustrated in

To save power the VLM circuit can be turned off completely, or it can be switched on and off at

regular intervals. However, detection takes some time and it is therefore recommended to leave

the circuitry on long enough for signals to settle. See

“VCC Level Monitor” on page 119

When VLM is active and voltage at V

CC

is above the selected trigger level operation will be as

normal and the VLM can be shut down for a short period of time. If voltage at V

CC

drops below

the selected threshold the VLM will either flag an interrupt or generate a reset, depending on the

configuration.

When the VLM has been configured to generate a reset at low supply voltage it will keep the

device in reset as long as V

CC

is below the reset level. See

Table 8-4 on page 34

for reset level

details. If supply voltage rises above the reset level the condition is removed and the MCU will

come out of reset, and initiate the power-up start-up sequence.

If supply voltage drops enough to trigger the POR then PORF is set after supply voltage has

been restored.

8.2.3

External Reset

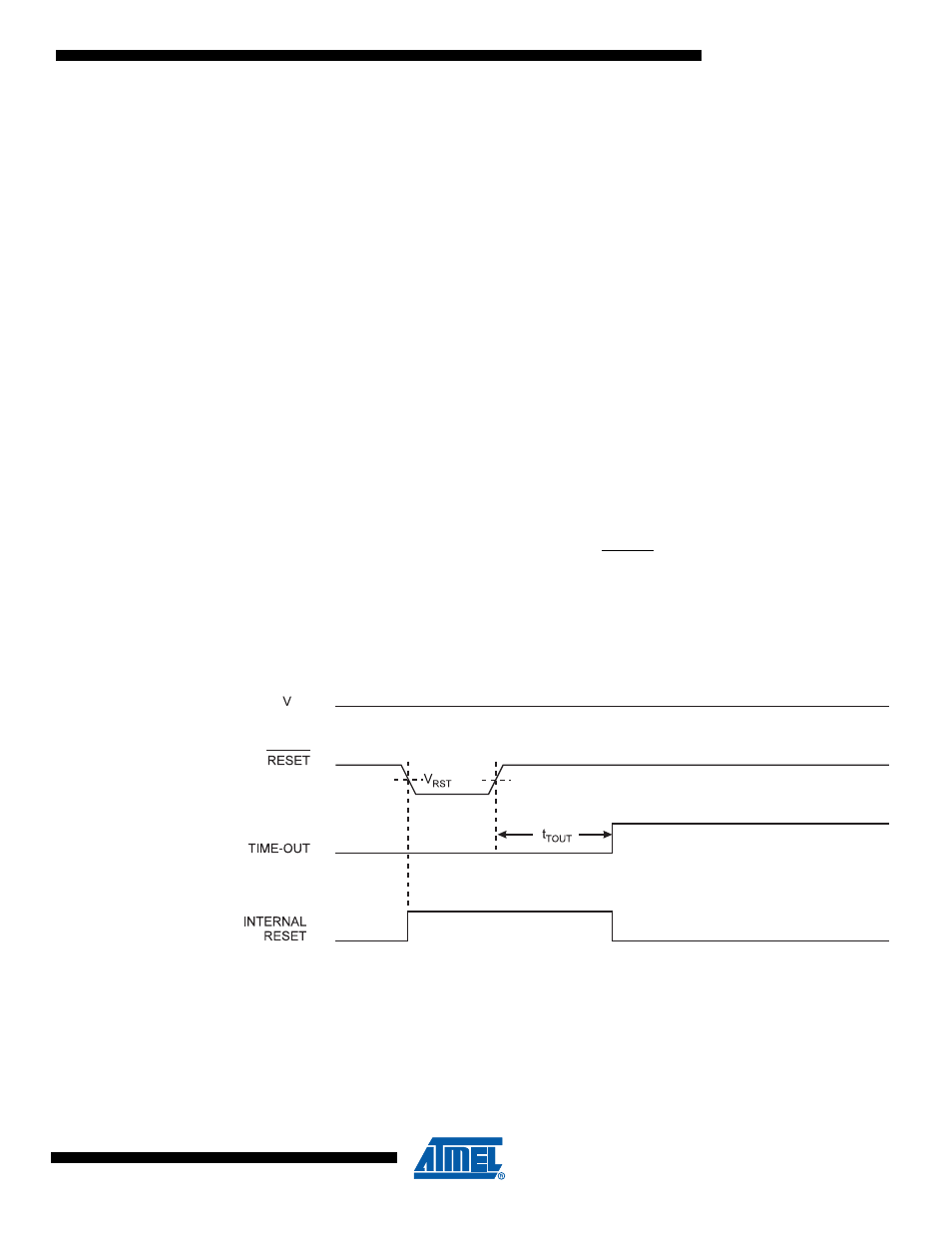

An External Reset is generated by a low level on the RESET pin if enabled. Reset pulses longer

than the minimum pulse width (see section

“System and Reset Characteristics” on page 119

)

will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to gen-

erate a reset. When the applied signal reaches the Reset Threshold Voltage – V

RST

– on its

positive edge, the delay counter starts the MCU after the time-out period – t

TOUT

–

has expired.

Figure 8-4.

External Reset During Operation

8.2.4

Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On

the falling edge of this pulse, the delay timer starts counting the time-out period t

TOUT

. See

for details on operation of the Watchdog Timer and

Table 16-4 on page 119

for details on

reset time-out.

CC