1 safety level 1, 2 safety level 2, 2 code examples – Rainbow Electronics ATtiny10 User Manual

Page 31

31

8127B–AVR–08/09

ATtiny4/5/9/10

8.3.1

Procedure for Changing the Watchdog Timer Configuration

The sequence for changing configuration differs between the two safety levels, as follows:

8.3.1.1

Safety Level 1

In this mode, the Watchdog Timer is initially disabled, but can be enabled by writing the WDE bit

to one without any restriction. A special sequence is needed when disabling an enabled Watch-

dog Timer. To disable an enabled Watchdog Timer, the following procedure must be followed:

1.

Write the signature for change enable of protected I/O registers to register CCP

2.

Within four instruction cycles, in the same operation, write WDE and WDP bits

8.3.1.2

Safety Level 2

In this mode, the Watchdog Timer is always enabled, and the WDE bit will always read as one. A

protected change is needed when changing the Watchdog Time-out period. To change the

Watchdog Time-out, the following procedure must be followed:

1.

Write the signature for change enable of protected I/O registers to register CCP

2.

Within four instruction cycles, write the WDP bit. The value written to WDE is irrelevant

8.3.2

Code Examples

The following code example shows how to turn off the WDT. The example assumes that inter-

rupts are controlled (e.g., by disabling interrupts globally) so that no interrupts will occur during

execution of these functions.

Note:

See

Table 8-1.

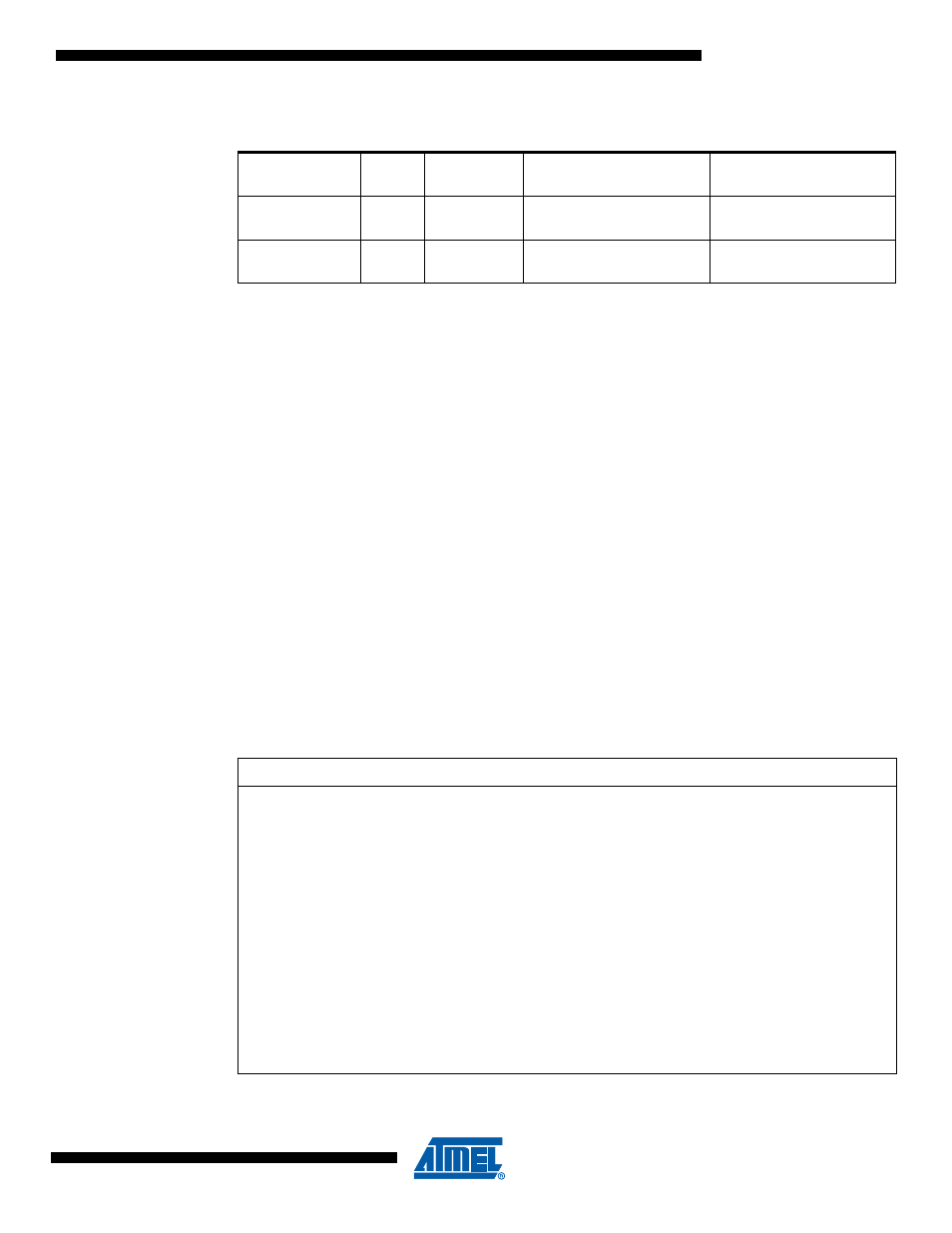

WDT Configuration as a Function of the Fuse Settings of WDTON

WDTON

Safety

Level

WDT

Initial State

How to

Disable the WDT

How to

Change Time-out

Unprogrammed

1

Disabled

Protected change

sequence

No limitations

Programmed

2

Enabled

Always enabled

Protected change

sequence

Assembly Code Example

WDT_off:

wdr

; Clear WDRF in RSTFLR

in

r16, RSTFLR

andi

r16, ~(1< out RSTFLR, r16 ; Write signature for change enable of protected I/O register ldi r16, 0xD8 out CCP, r16 ; Within four instruction cycles, turn off WDT ldi r16, (0< out WDTCSR, r16 ret