3 clkpsr – clock prescale register – Rainbow Electronics ATtiny10 User Manual

Page 22

22

8127B–AVR–08/09

ATtiny4/5/9/10

6.5.3

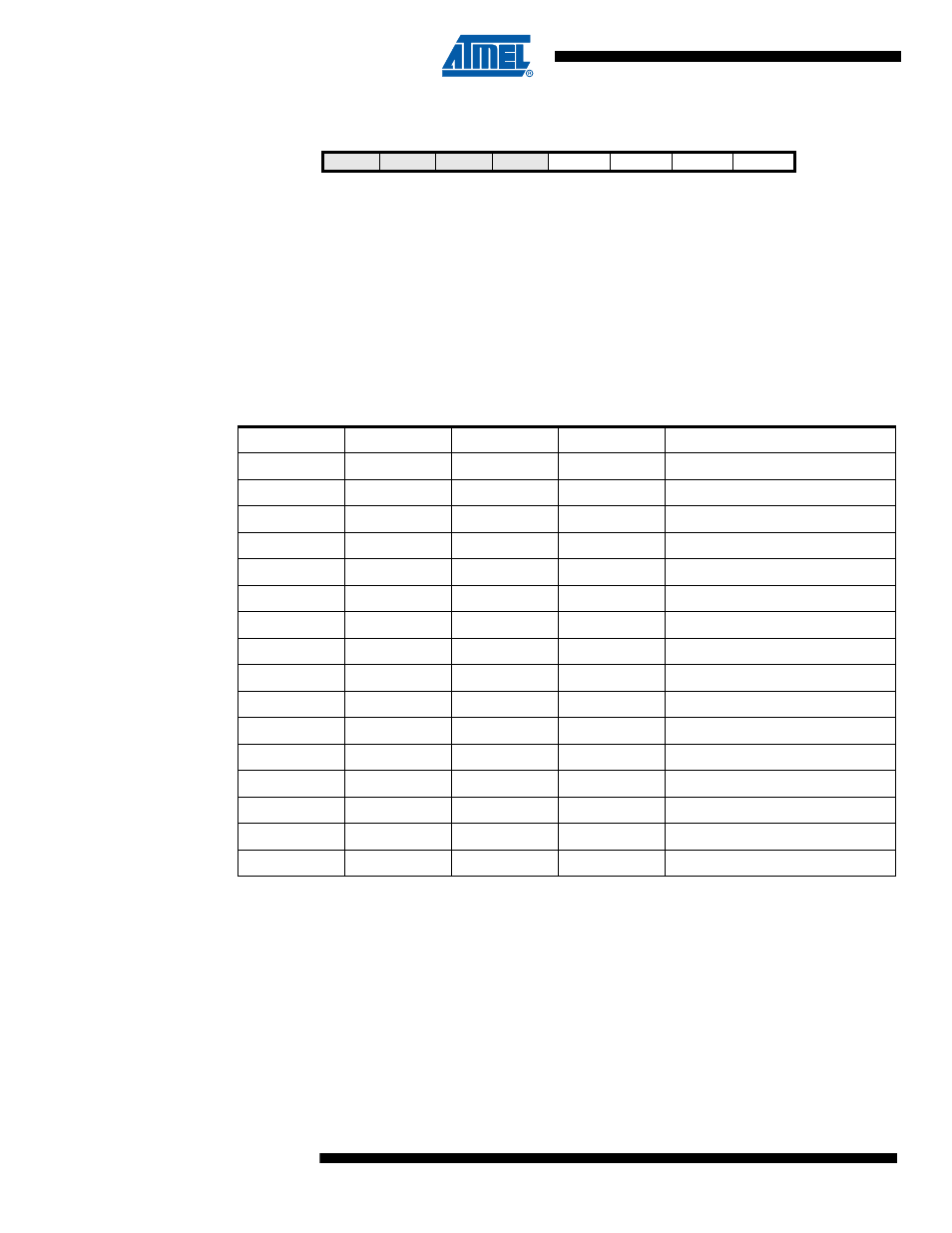

CLKPSR – Clock Prescale Register

• Bits 7:4 – Res: Reserved Bits

These bits are reserved and will always read as zero.

• Bits 3:0 – CLKPS[3:0]: Clock Prescaler Select Bits 3 - 0

These bits define the division factor between the selected clock source and the internal system

clock. These bits can be written at run-time to vary the clock frequency and suit the application

requirements. As the prescaler divides the master clock input to the MCU, the speed of all syn-

chronous peripherals is reduced accordingly. The division factors are given in

Table 6-4

.

To avoid unintentional changes of clock frequency, a protected change sequence must be fol-

lowed to change the CLKPS bits:

1.

Write the signature for change enable of protected I/O register to register CCP

2.

Within four instruction cycles, write the desired value to CLKPS bits

At start-up, CLKPS bits are reset to 0b0011 to select the clock division factor of 8. If the selected

clock source has a frequency higher than the maximum allowed the application software must

make sure a sufficient division factor is used. To make sure the write procedure is not inter-

rupted, interrupts must be disabled when changing prescaler settings.

Bit

7

6

5

4

3

2

1

0

–

–

–

–

CLKPS3

CLKPS2

CLKPS1

CLKPS0

CLKPSR

Read/Write

R

R

R

R

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

1

1

Table 6-4.

Clock Prescaler Select

CLKPS3

CLKPS2

CLKPS1

CLKPS0

Clock Division Factor

0

0

0

0

1

0

0

0

1

2

0

0

1

0

4

0

0

1

1

8 (default)

0

1

0

0

16

0

1

0

1

32

0

1

1

0

64

0

1

1

1

128

1

0

0

0

256

1

0

0

1

Reserved

1

0

1

0

Reserved

1

0

1

1

Reserved

1

1

0

0

Reserved

1

1

0

1

Reserved

1

1

1

0

Reserved

1

1

1

1

Reserved