2 didr0 – digital input disable register 0 – Rainbow Electronics ATtiny10 User Manual

Page 82

82

8127B–AVR–08/09

ATtiny4/5/9/10

• Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined

by ACIS1 and ACIS0. The analog comparator interrupt routine is executed if the ACIE bit is set

and the I-bit in SREG is set. ACI is cleared by hardware when executing the corresponding inter-

rupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

• Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is written logic one, the Analog Comparator interrupt request is enabled.

When written logic zero, the interrupt request is disabled.

• Bit 2 – ACIC: Analog Comparator Input Capture Enable

When set, this bit enables the input capture function in Timer/Counter0 to be triggered by the

analog comparator. In this case, the comparator output is directly connected to the input capture

front-end logic, using the noise canceler and edge select features of the Timer/Counter0 input

capture interrupt. To make the comparator trigger the Timer/Counter0 input capture interrupt,

the ICIE1 bit in “TIMSK0 – Timer/Counter Interrupt Mask Register 0” must be set.

When this bit is cleared, no connection between the analog comparator and the input capture

function exists.

• Bits 1:0 – ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events that trigger the analog comparator interrupt. The

different settings are shown in

.

When changing the ACIS1/ACIS0 bits, the analog comparator Interrupt must be disabled by

clearing its Interrupt Enable bit in “ACSR – Analog Comparator Control and Status Register”.

Otherwise an interrupt can occur when the bits are changed.

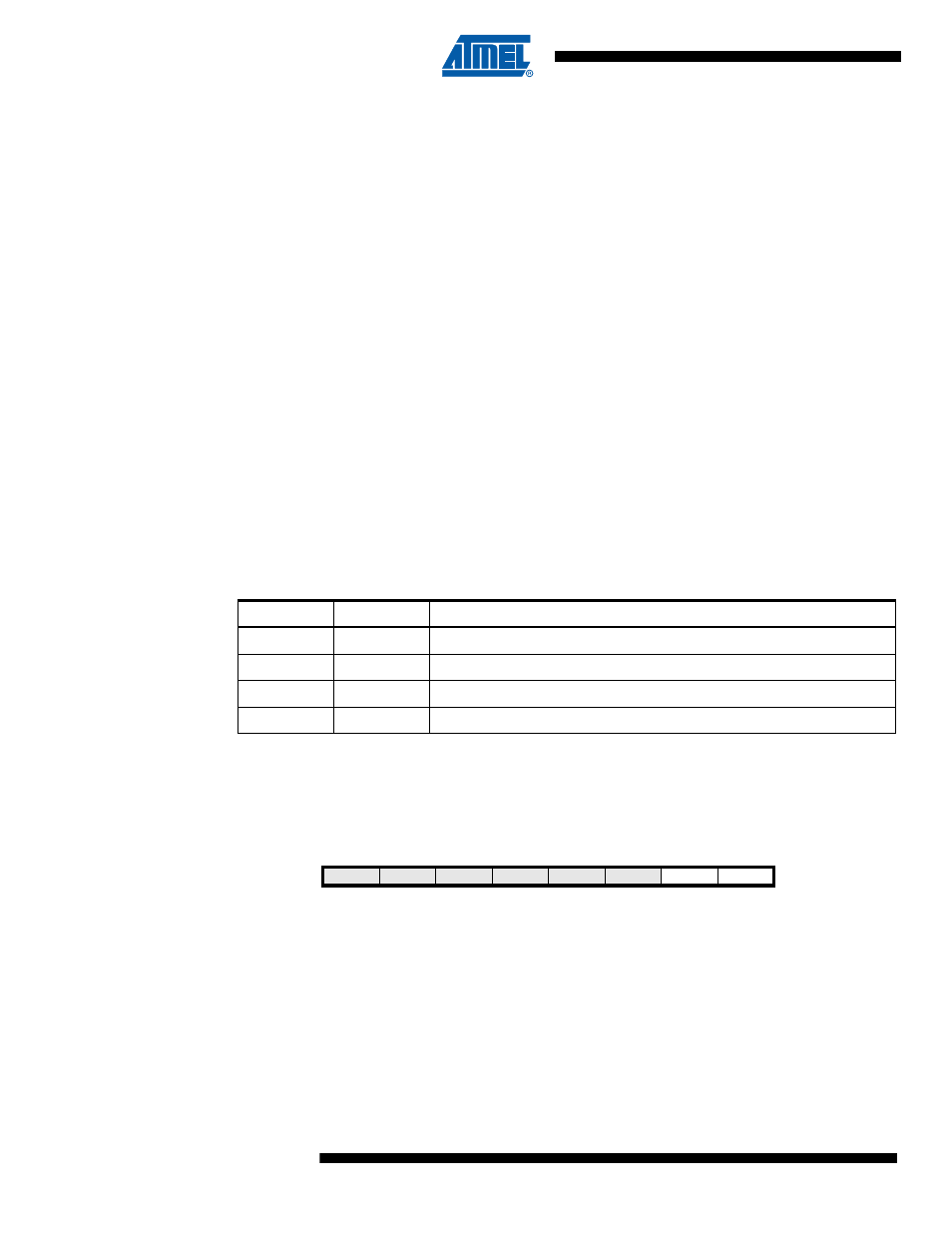

12.1.2

DIDR0 – Digital Input Disable Register 0

• Bits 1:0 – ADC1D, ADC0D: Digital Input Disable

When this bit is set, the digital input buffer on pin AIN1 (ADC1) / AIN0 (ADC0) is disabled and

the corresponding PIN register bit will read as zero. When used as an analog input but not

required as a digital input the power consumption in the digital input buffer can be reduced by

writing this bit to logic one.

Table 12-1.

Selecting Source for Analog Comparator Interrupt.

ACIS1

ACIS0

Interrupt Mode

0

0

Comparator Interrupt on Output Toggle.

0

1

Reserved

1

0

Comparator Interrupt on Falling Output Edge.

1

1

Comparator Interrupt on Rising Output Edge.

Bit

7

6

5

4

3

2

1

0

0x17

–

–

–

–

–

–

ADC1D

ADC0D

DIDR0

Read/Write

R

R

R

R

R

R

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0