8 register description, 1 ccp – configuration change protection register, 2 sph and spl — stack pointer register – Rainbow Electronics ATtiny10 User Manual

Page 12: 3 sreg – status register

12

8127B–AVR–08/09

ATtiny4/5/9/10

4.8

Register Description

4.8.1

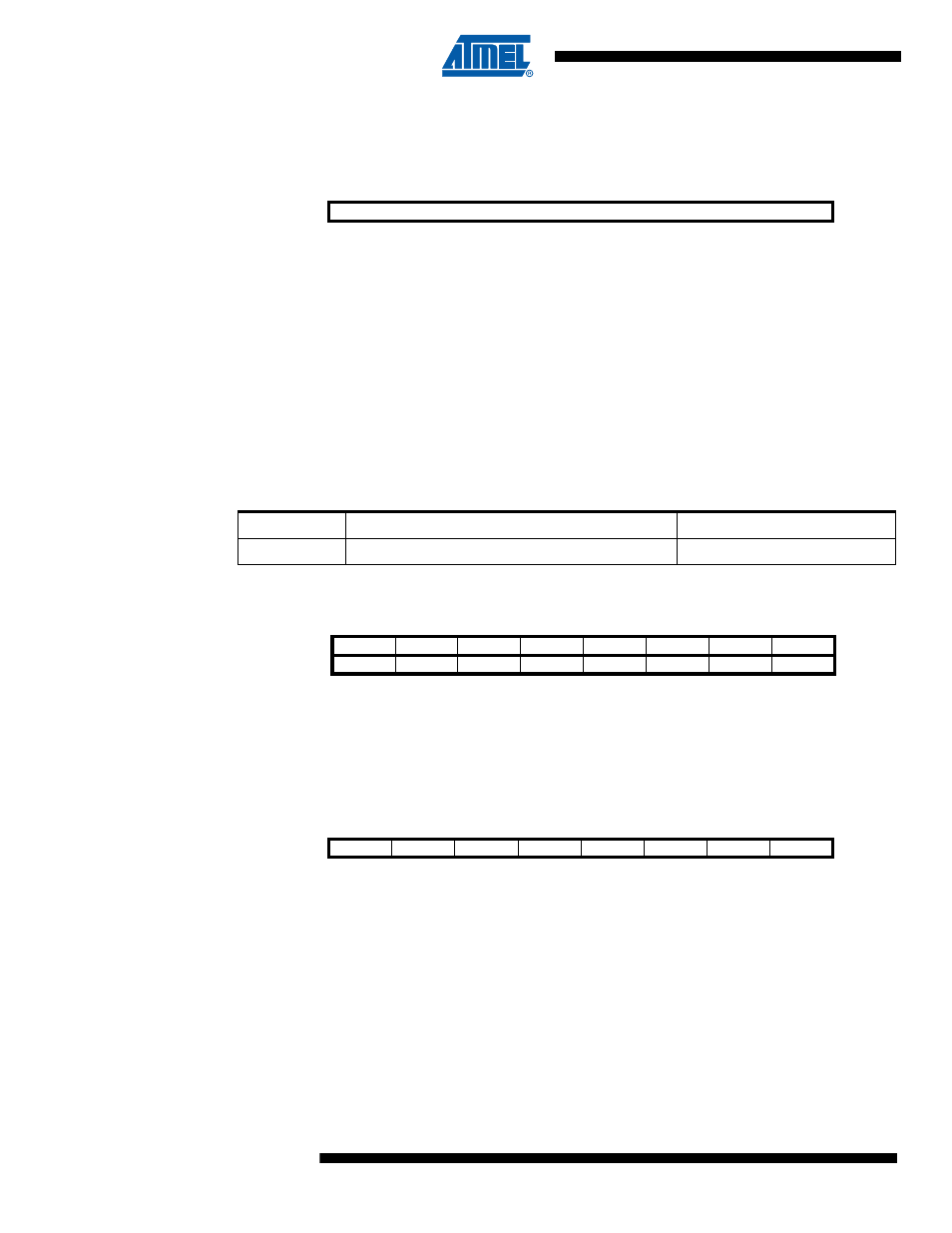

CCP – Configuration Change Protection Register

• Bits 7:0 – CCP[7:0] – Configuration Change Protection

In order to change the contents of a protected I/O register the CCP register must first be written

with the correct signature. After CCP is written the protected I/O registers may be written to dur-

ing the next four CPU instruction cycles. All interrupts are ignored during these cycles. After

these cycles interrupts are automatically handled again by the CPU, and any pending interrupts

will be executed according to their priority.

When the protected I/O register signature is written, CCP[0] will read as one as long as the pro-

tected feature is enabled, while CCP[7:1] will always read as zero.

shows the signatures that are in recognised.

4.8.2

SPH and SPL — Stack Pointer Register

4.8.3

SREG – Status Register

• Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual inter-

rupt enable control is then performed in separate control registers. If the Global Interrupt Enable

Register is cleared, none of the interrupts are enabled independent of the individual interrupt

enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by

the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by

the application with the SEI and CLI instructions, as described in the document “AVR Instruction

Set” and

“Instruction Set Summary” on page 151

• Bit 6 – T: Bit Copy Storage

Bit

7

6

5

4

3

2

1

0

0x3C

CCP[7:0]

CCP

Read/Write

W

W

W

W

W

W

W

W

Initial Value

0

0

0

0

0

0

0

0

Table 4-1.

Signatures Recognised by the Configuration Change Protection Register

Signature

Group

Description

0xD8

IOREG: CLKMSR, CLKPSR, WDTCSR

Protected I/O register

Bit

15

14

13

12

11

10

9

8

0x3E

SP15

SP14

SP13

SP12

SP11

SP10

SP9

SP8

SPH

0x3D

SP7

SP6

SP5

SP4

SP3

SP2

SP1

SP0

SPL

7

6

5

4

3

2

1

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

Initial Value

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

RAMEND

Bit

7

6

5

4

3

2

1

0

0x3F

I

T

H

S

V

N

Z

C

SREG

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0