3 tccr0c – timer/counter0 control register c – Rainbow Electronics ATtiny10 User Manual

Page 76

76

8127B–AVR–08/09

ATtiny4/5/9/10

When a capture is triggered according to the ICES0 setting, the counter value is copied into the

Input Capture Register (ICR0). The event will also set the Input Capture Flag (ICF0), and this

can be used to cause an Input Capture Interrupt, if this interrupt is enabled.

When the ICR0 is used as TOP value (see description of the WGM03:0 bits located in the

TCCR0A and the TCCR0B Register), the ICP0 is disconnected and consequently the Input Cap-

ture function is disabled.

• Bit 5 – Reserved Bit

This bit is reserved for future use. For ensuring compatibility with future devices, this bit must be

written to zero when TCCR0B is written.

• Bits 4:3 – WGM03:2: Waveform Generation Mode

See

“TCCR0A – Timer/Counter0 Control Register A” on page 73

• Bits 2:0 – CS02:0: Clock Select

The three Clock Select bits set the clock source to be used by the Timer/Counter, see

Figure 11-

12

and

Figure 11-13

.

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the

counter even if the pin is configured as an output. This feature allows software control of the

counting.

11.11.3

TCCR0C – Timer/Counter0 Control Register C

• Bit 7 – FOC0A: Force Output Compare for Channel A

• Bit 6 – FOC0B: Force Output Compare for Channel B

The FOC0A/FOC0B bits are only active when the WGM03:0 bits specifies a non-PWM mode.

However, for ensuring compatibility with future devices, these bits must be set to zero when

TCCR0A is written when operating in a PWM mode. When writing a logical one to the

FOC0A/FOC0B bit, an immediate compare match is forced on the Waveform Generation unit.

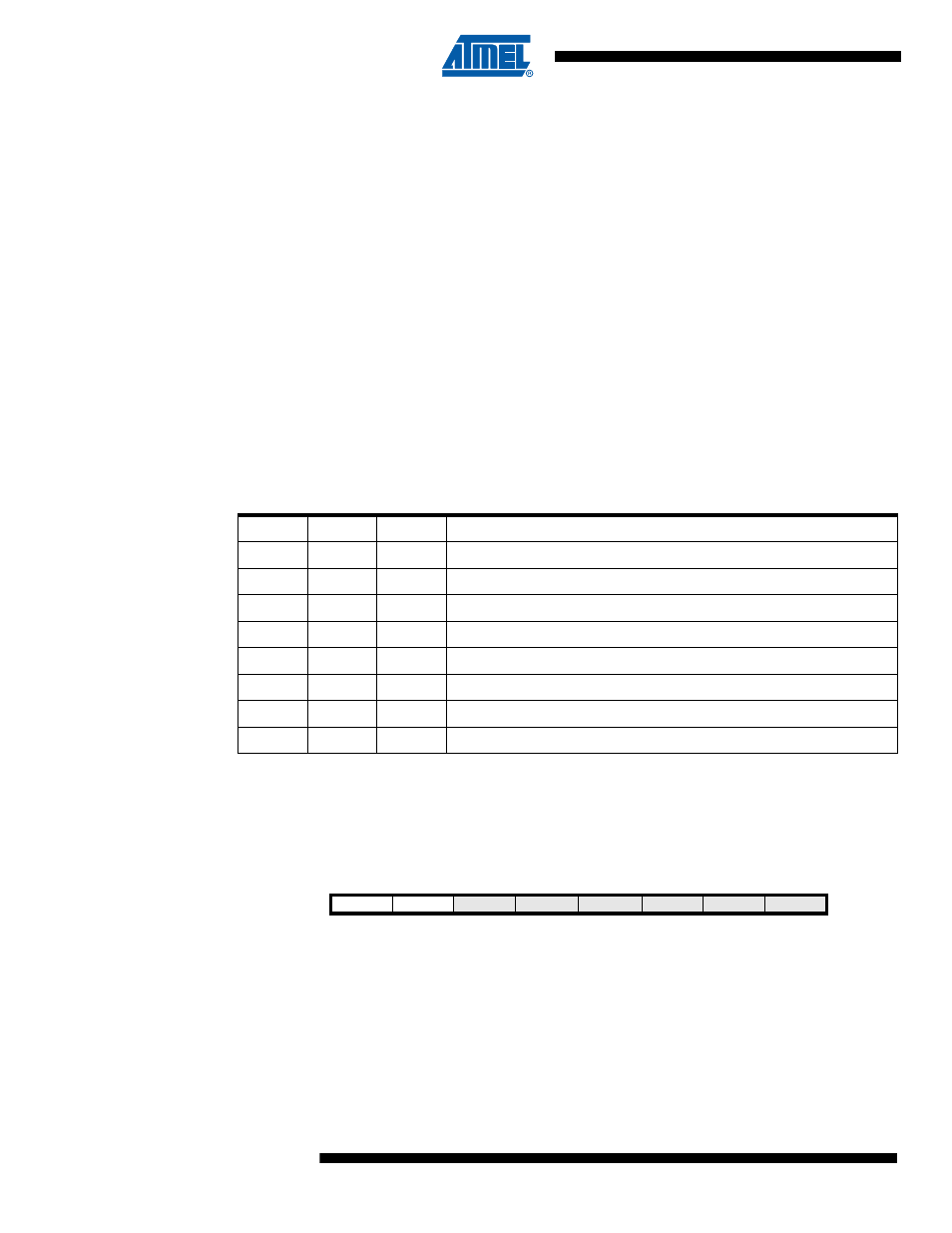

Table 11-6.

Clock Select Bit Description

CS02

CS01

CS00

Description

0

0

0

No clock source (Timer/Counter stopped)

0

0

1

clk

I/O

/1 (No prescaling)

0

1

0

clk

I/O

/8 (From prescaler)

0

1

1

clk

I/O

/64 (From prescaler)

1

0

0

clk

I/O

/256 (From prescaler)

1

0

1

clk

I/O

/1024 (From prescaler)

1

1

0

External clock source on T0 pin. Clock on falling edge

1

1

1

External clock source on T0 pin. Clock on rising edge

Bit

7

6

5

4

3

2

1

0

0x2C

FOC0A

FOC0B

–

–

–

–

–

–

TCCR0C

Read/Write

W

W

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0