I/o ports, 1 overview – Rainbow Electronics ATtiny10 User Manual

Page 40

40

8127B–AVR–08/09

ATtiny4/5/9/10

10. I/O Ports

10.1

Overview

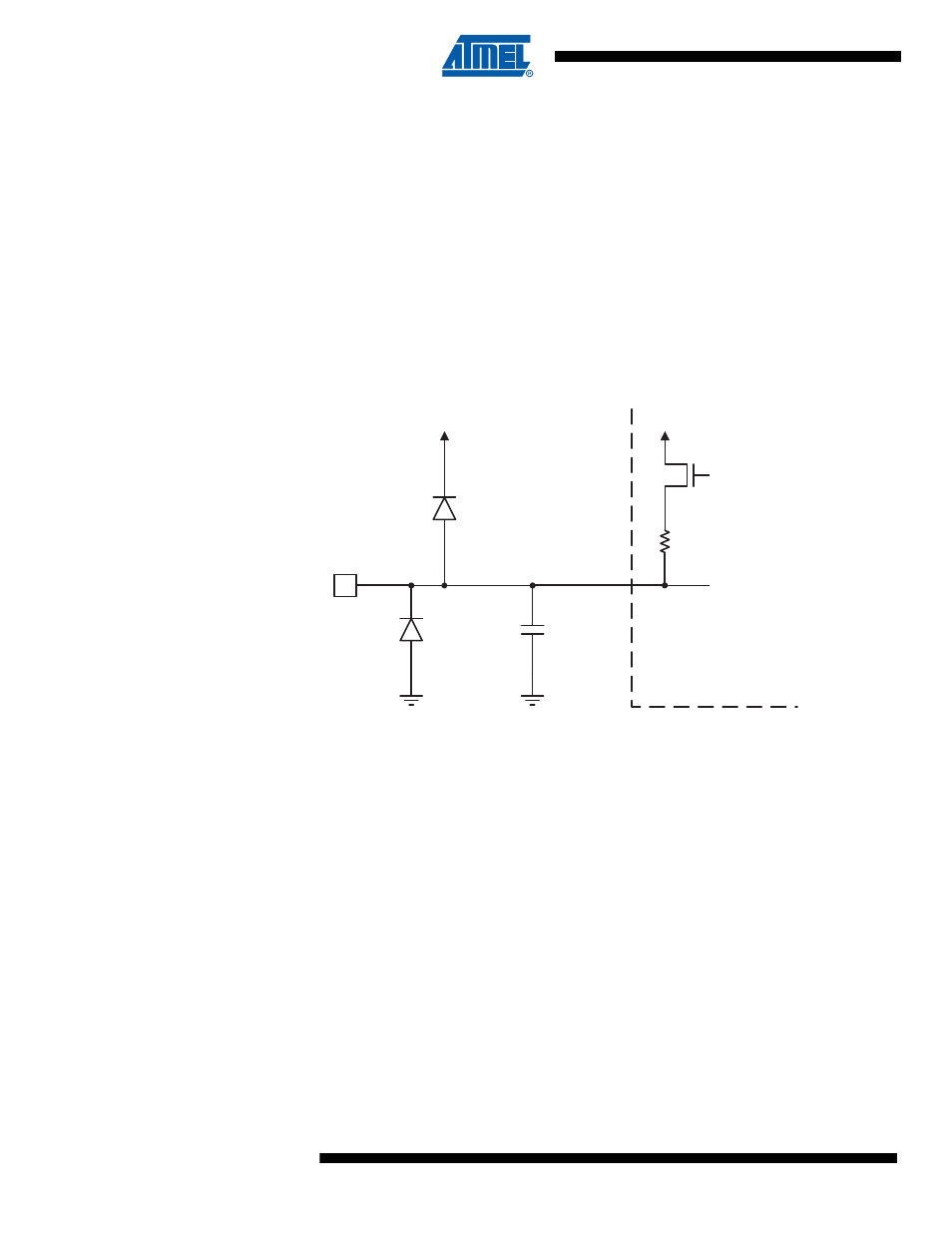

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports.

This means that the direction of one port pin can be changed without unintentionally changing

the direction of any other pin with the SBI and CBI instructions. The same applies when chang-

ing drive value (if configured as output) or enabling/disabling of pull-up resistors. Each output

buffer has symmetrical drive characteristics with both high sink and source capability. The pin

driver is strong enough to drive LED displays directly. All port pins have individually selectable

pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to

both V

CC

and Ground as indicated in

Figure 10-1 on page 40

. See

“Electrical Characteristics” on

for a complete list of parameters.

Figure 10-1. I/O Pin Equivalent Schematic

All registers and bit references in this section are written in general form. A lower case “x” repre-

sents the numbering letter for the port, and a lower case “n” represents the bit number. However,

when using the register or bit defines in a program, the precise form must be used. For example,

PORTB3 for bit no. 3 in Port B, here documented generally as PORTxn. The physical I/O Regis-

ters and bit locations are listed in

“Register Description” on page 50

Four I/O memory address locations are allocated for each port, one each for the Data Register –

PORTx, Data Direction Register – DDRx, Pull-up Enable Register – PUEx, and the Port Input

Pins – PINx. The Port Input Pins I/O location is read only, while the Data Register, the Data

Direction Register, and the Pull-up Enable Register are read/write. However, writing a logic one

to a bit in the PINx Register, will result in a toggle in the corresponding bit in the Data Register.

Using the I/O port as General Digital I/O is described in

“Ports as General Digital I/O” on page

. Most port pins are multiplexed with alternate functions for the peripheral features on the

device. How each alternate function interferes with the port pin is described in

. Refer to the individual module sections for a full description of the alter-

nate functions.

Note that enabling the alternate function of some of the port pins does not affect the use of the

other pins in the port as general digital I/O.

C

pin

Logic

R

pu

See Figure

"General Digital I/O" for

Details

Pxn