1 power-on reset, 2 vcc level monitoring – Rainbow Electronics ATtiny10 User Manual

Page 28

28

8127B–AVR–08/09

ATtiny4/5/9/10

8.2.1

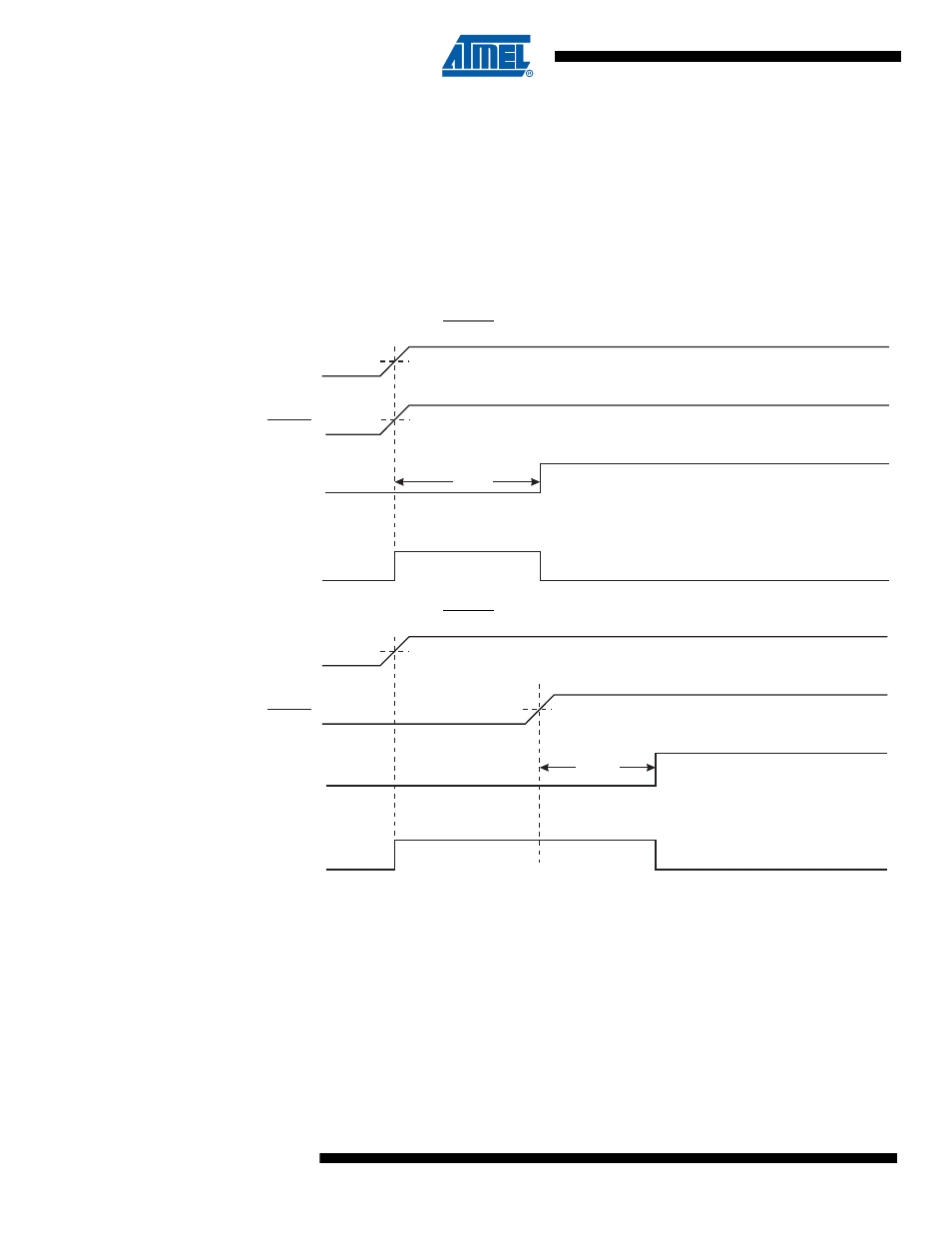

Power-on Reset

A Power-on Reset (POR) pulse is generated by an on-chip detection circuit. The detection level

is defined in section

“System and Reset Characteristics” on page 119

. The POR is activated

whenever V

CC

is below the detection level. The POR circuit can be used to trigger the Start-up

Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the

Power-on Reset threshold voltage invokes the delay counter, which determines how long the

device is kept in reset after V

CC

rise. The reset signal is activated again, without any delay, when

V

CC

decreases below the detection level.

Figure 8-2.

MCU Start-up, RESET Tied to V

CC

Figure 8-3.

MCU Start-up, RESET Extended Externally

8.2.2

V

CC

Level Monitoring

ATtiny4/5/9/10 have a V

CC

Level Monitoring (VLM) circuit that compares the voltage level at the

V

CC

pin against fixed trigger levels. The trigger levels are set with VLM2:0 bits, see

VCC Level Monitoring Control and Status register” on page 33

.

The VLM circuit provides a status flag, VLMF, that indicates if voltage on the V

CC

pin is below the

selected trigger level. The flag can be read from VLMCSR, but it is also possible to have an

interrupt generated when the VLMF status flag is set. This interrupt is enabled by the VLMIE bit

in the VLMCSR register. The flag can be cleared by changing the trigger level or by writing it to

zero. The flag is automatically cleared when the voltage at V

CC

rises back above the selected

trigger level.

V

RESET

TIME-OUT

INTERNAL

RESET

t

TOUT

V

POT

V

RST

CC

RESET

TIME-OUT

INTERNAL

RESET

t

TOUT

V

POT

V

RST

V

CC