Rainbow Electronics ATtiny10 User Manual

Page 87

87

8127B–AVR–08/09

ATtiny4/5/9/10

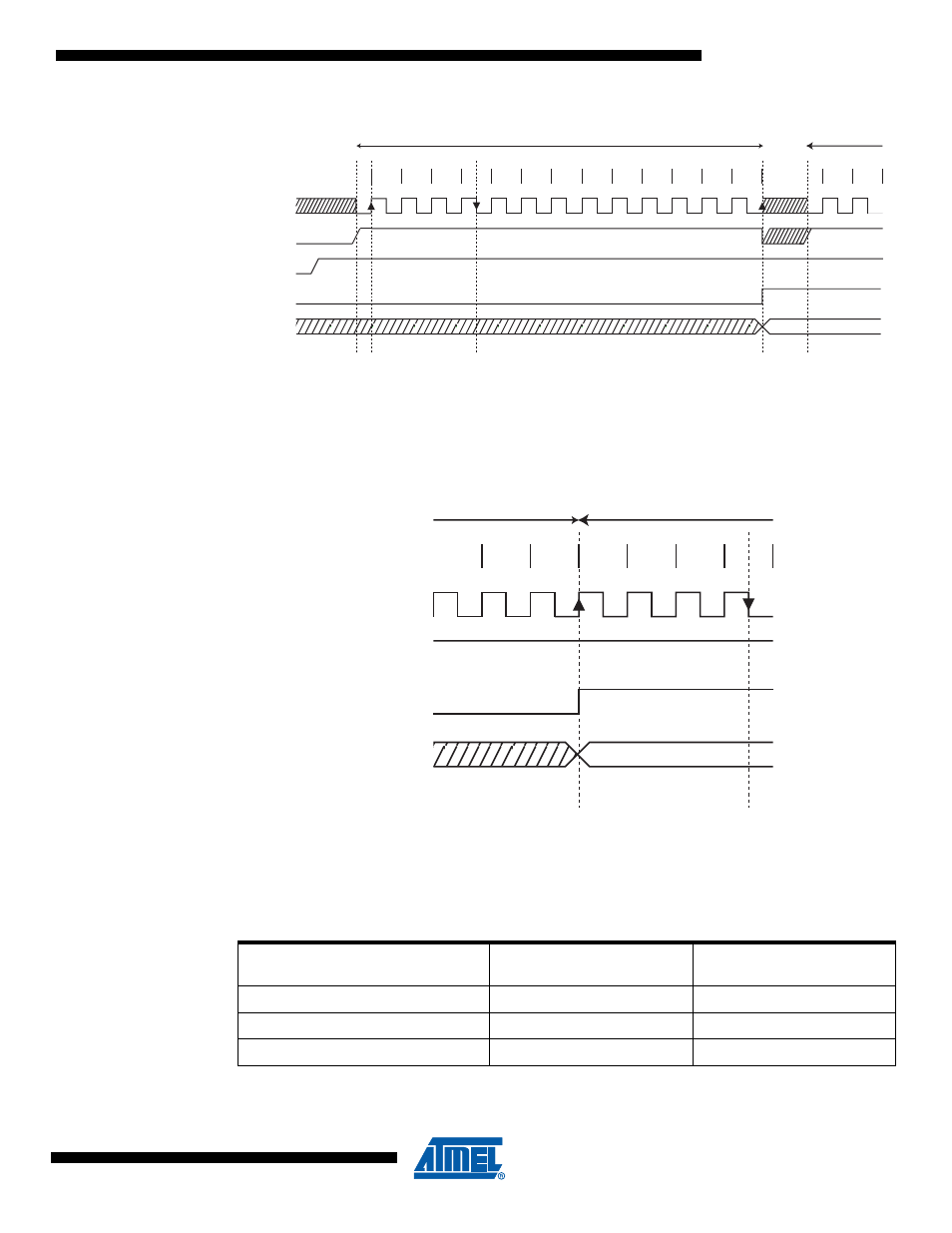

Figure 13-6. ADC Timing Diagram, Auto Triggered Conversion

), a new conversion will be started immediately after the

conversion completes, while ADSC remains high.

Figure 13-7. ADC Timing Diagram, Free Running Conversion

For a summary of conversion times, see

Table 13-1

.

Table 13-1.

ADC Conversion Time

Condition

Sample & Hold (Cycles from

Start of Conversion)

Conversion Time (Cycles)

First conversion

16.5

25

Normal conversions

3.5

13

Auto Triggered conversions

4

13.5

1

2

3

4

5

6

7

8

9

10

11

12

13

Conversion Result

ADC Clock

Trigger

Source

ADIF

ADCL

Cycle Number

1

2

One Conversion

Next Conversion

Conversion

Complete

Prescaler

Reset

ADATE

Prescaler

Reset

Sample &

Hold

MUX

Update

11

12

13

Conversion Result

ADC Clock

ADSC

ADIF

ADCL

Cycle Number

1

2

One Conversion

Next Conversion

3

4

Conversion complete

Sample & Hold

MUX update

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)