Texas Instruments TMS320C3x User Manual

Page 744

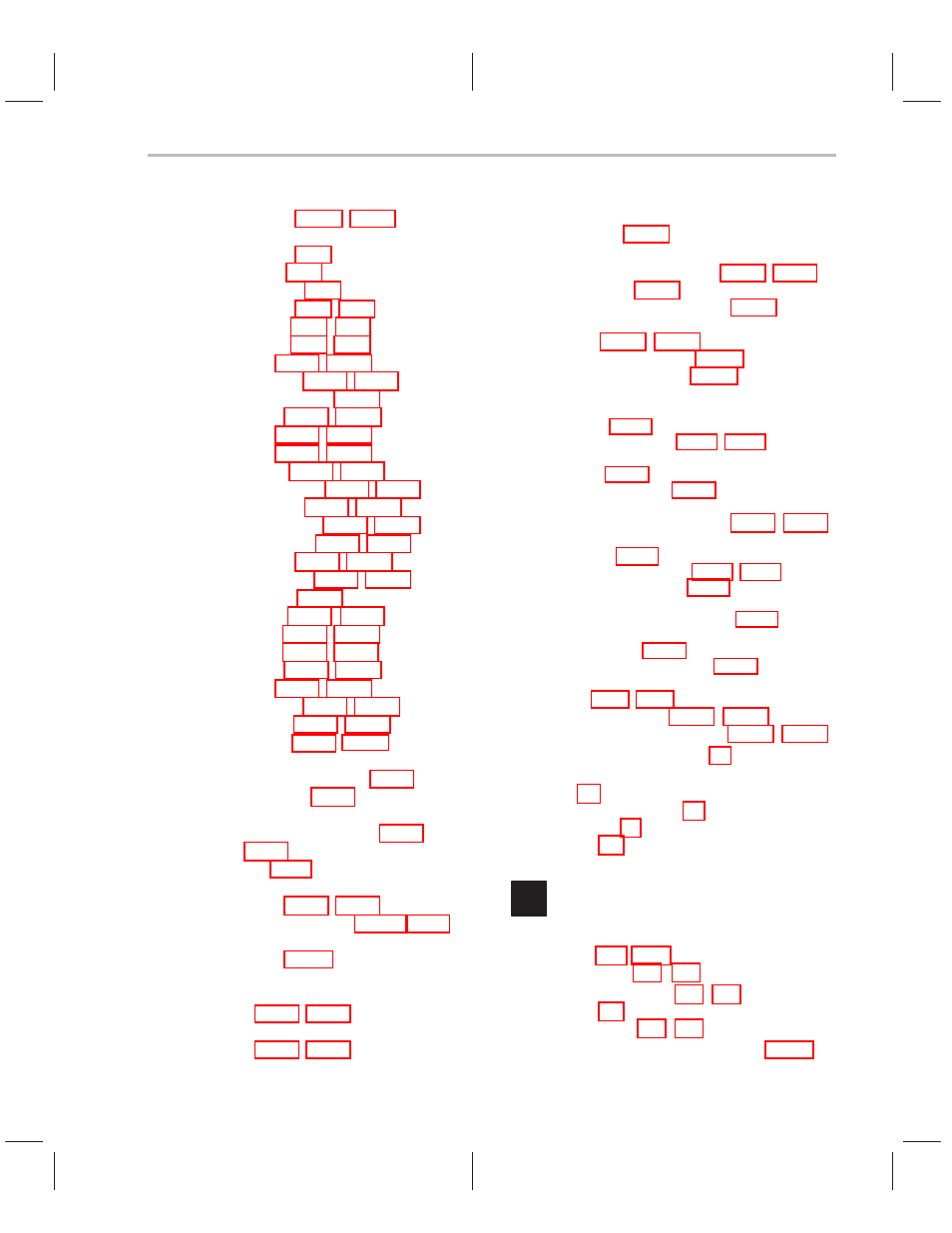

Index

Index-3

assembly language instructions (continued)

normalize (NORM)

parallel instructions

ABSF and STF

ABSI and STI

ADDF3 and STF

ADDI3 and STI

AND3 and STI

ASH3 and STI

FIX and STI

FLOAT and STF

LDF and LDF

13-119–13-120

LDF and STF

LDI and LDI

LDI and STI

LSH3 and STI

MPYF3 and ADDF3

MPYF3 and STF

MPYF3 and SUBF3

MPYI3 and ADDI3

MPYI3 and STI

MPYI3 and SUBI3

NEGF and STF

NEGI and STI

NOT and STI

OR3 and STI

STF and STF

STI and STI

SUBF3 and STF

SUBI3 and STI

XOR3 and STI

POP

floating-point value (POPF)

integer instruction

PUSH

floating-point value (PUSHF)

integer

register syntax

repeat

block (RPTB)

single instruction (RPTS)

restore clock to regular speed

(MAXSPEED)

return

from interrupt conditionally (RETI-

cond)

from subroutine conditionally (RETS-

cond)

assembly language instructions (continued)

rotate

left (ROL)

assembly language instructions (continued)

left through carry (ROLC)

right (ROR)

right through carry (RORC)

round floating-point value

(RND)

signal, interlocked (SIGI)

software interrupt (SWI)

store

floating-point value

(STF)

interlocked (STFI)

integer

(STI)

interlocked (STII)

subtract

floating-point value (SUBF)

integer

(SUBI)

conditionally (SUBC)

with borrow (SUBB)

reverse

floating-point value (SUBRF)

integer

(SUBRI)

with borrow (SUBRB)

symbols used to define instruc-

tions

test bit fields (TSTB)

trap conditionally (TRAPcond)

auxiliary (AR7–AR0) registers

auxiliary register

ALUs

arithmetic unit (ARAU)

definition

definition

B

bank switching

example

programmable

bit-reversed, addressing

definition

FFT algorithms

bitwise-exclusive OR instruction (XOR)