External ready timing improvement, 9 external ready timing improvement – Texas Instruments TMS320C3x User Manual

Page 341

External Ready Timing Improvement

10-38

10.9 External Ready Timing Improvement

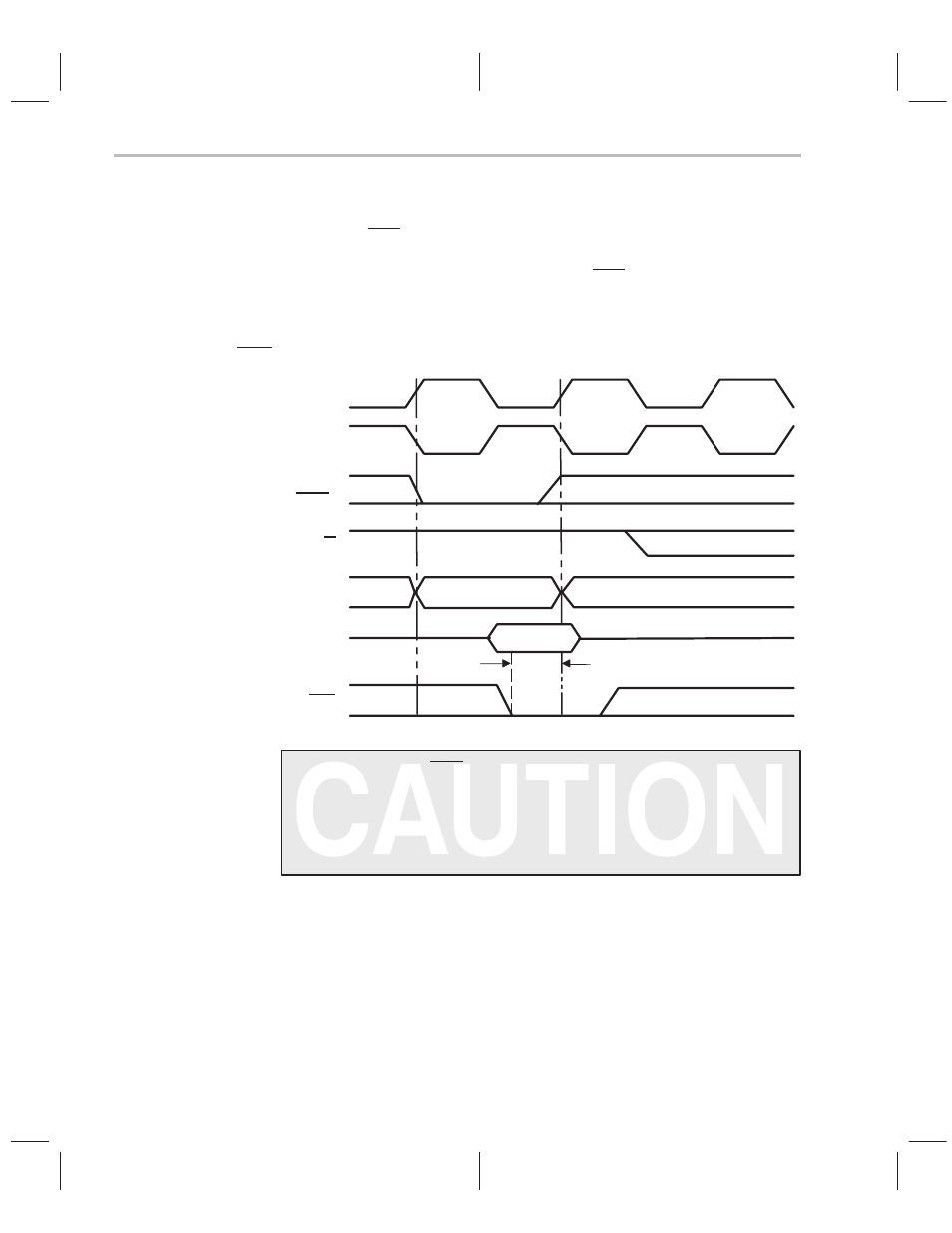

The ready (RDY) timing should relate to the H1 low signal as shown in

Figure 10–22. This is equivalent to the ’C4x ready timing, which increases the

time between valid address and the sampling of RDY. This facilitates the memory

hardware interface by allowing a longer address decode-circuit response time to

generate a ready signal.

Figure 10–22. RDY Timing for Memory Read

RDY

D

A

R/W

STRBx

H1

H3

Data

Address

tsu(RDY)

Do not change the RDY signal during its setup time [

t

su(RDY)].

See also other documents in the category Texas Instruments Hardware:

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TMS320TCI648x (256 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)