Texas Instruments TMS320C3x User Manual

Page 477

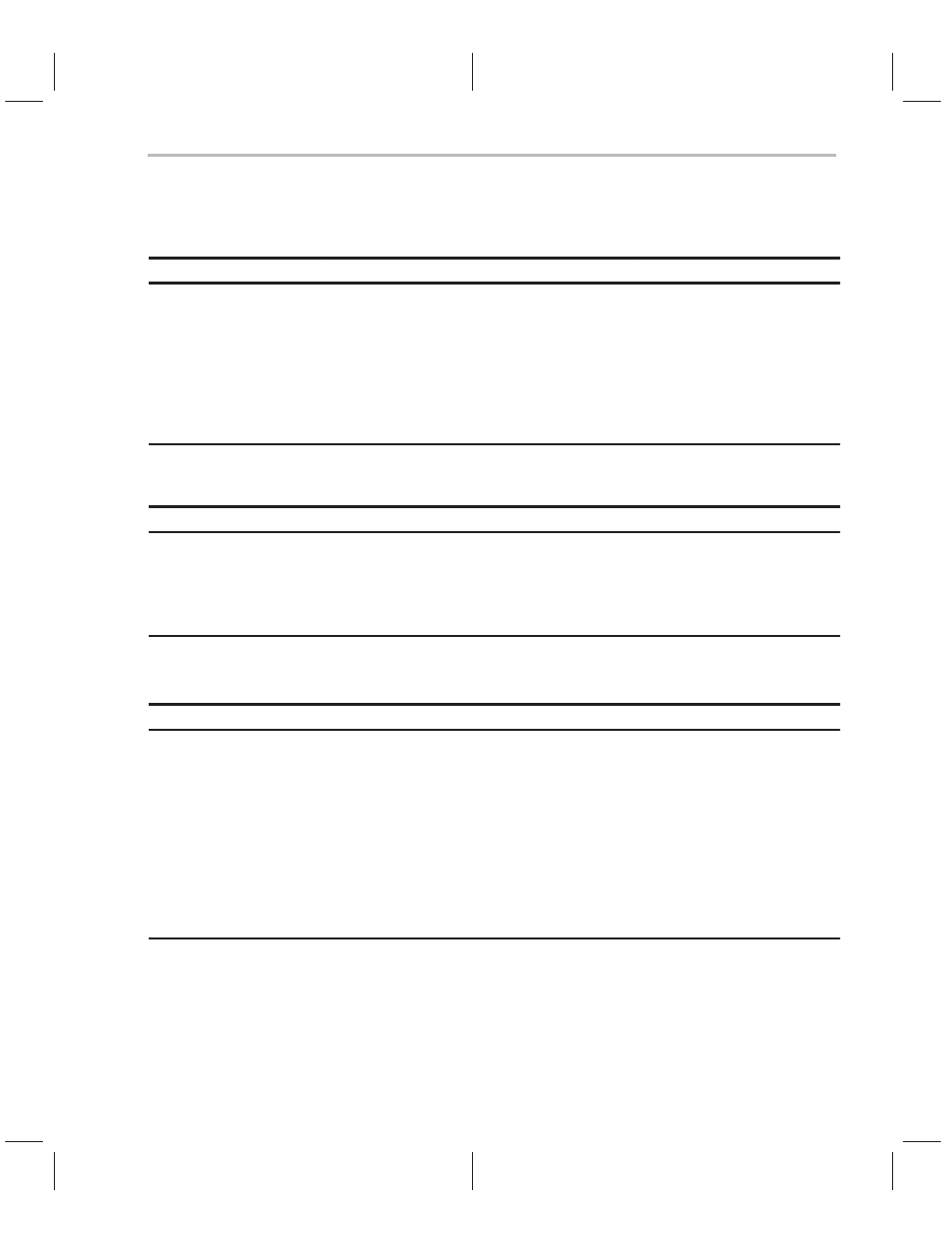

Parallel Instruction Set Summary

13-19

Assembly Language Instructions

Table 13–9. Parallel Instruction Set Summary (Continued)

(a) Parallel arithmetic with store instructions (Continued)

Mnemonic

Description

Operation

SUBF3

|| STF

Subtract floating-point value

src1 – src2

→

dst1

||

src3

→

dst2

SUBI3

|| STI

Subtract integer

src1 – src2

→

dst1

||

src3

→

dst2

XOR3

|| STI

Bitwise-exclusive OR

src1 XOR src2

→

dst1

||

src3

→

dst2

(b) Parallel load instructions

Mnemonic

Description

Operation

LDF

|| LDF

Load floating-point value

src2

→

dst1

||

src4

→

dst2

LDI

||

LDI

Load integer

src2

→

dst1

||

src4

→

dst2

(c) Parallel multiply and add/subtract instructions

Mnemonic

Description

Operation

MPYF3

|| ADDF3

Multiply and add floating-point value

op1 x op2

→

op3

||

op4 + op5

→

op6

MPYF3

|| SUBF3

Multiply and subtract floating-point value

op1 x op2

→

op3

||

op4 – op5

→

op6

MPYI3

|| ADDI3

Multiply and add integer

op1 x op2

→

op3

||

op4 + op5

→

op6

MPYI3

|| SUBI3

Multiply and subtract integer

op1 x op2

→

op3

||

op4 – op5

→

op6

Legend:

count

register addr (R7–R0)

op3

register addr (R0 or R1)

dst1

register addr (R7–R0)

op6

register addr (R2 or R3)

dst2

indirect addr (

disp = 0, 1, IR0, IR1)

src1

register addr (R7–R0)

op1, op2, op4, and op5

src2

indirect addr (

disp = 0, 1, IR0, IR1)

Any two of these operands must be

src3

register addr (R7–R0)

specified using register addr; the remaining

two must be specified using indirect.