Program memory access – Texas Instruments TMS320C3x User Manual

Page 307

TMS320C32 Memory Overview

10-4

IOSTRB can access 32-bit data from 32-bit wide memory. It does not have the

flexibility of STRB0 and STRB1 since it is composed of a single signal:

IOSTRB. IOSTRB bus cycles are different from those of STRB0 and STRB1

and are discussed in Section 10.10. This timing difference accomodates

slower I/O peripherals.

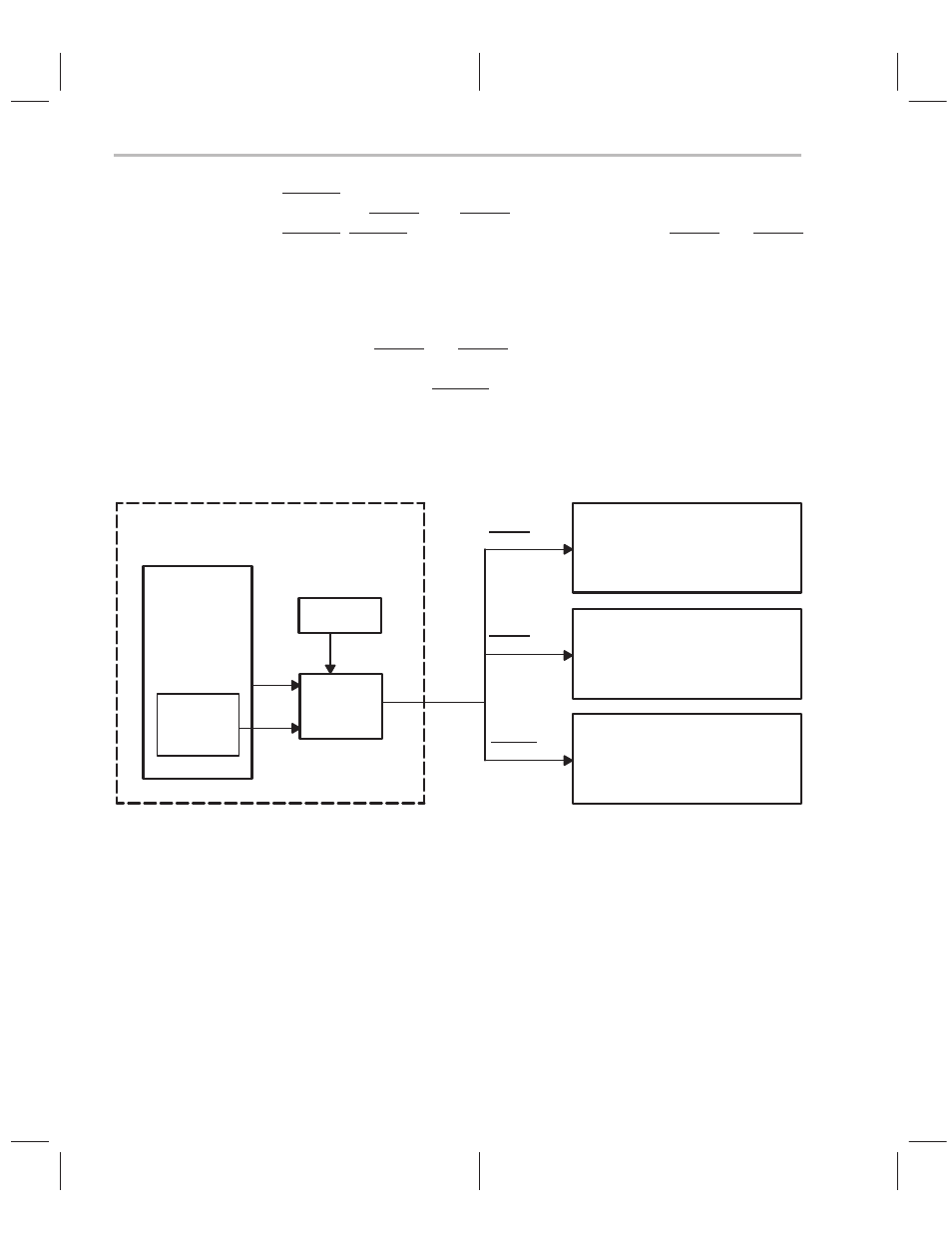

The ’C32 memory interface parallel bus implements three mutually-exclusive

address spaces distinguished via three separate control signals as shown in

Figure 10–1. STRB0 and STRB1 support 8-, 16-, or 32-bit data access in 8-,

16-, 32-bit-wide external memory and 16-, 32-bit program access in 16-/32-bit-

wide external memory. IOSTRB address space supports 32-bit data/program ac-

cess in 32-bit-wide external memory. Internally, the ’C32 has a 32-bit architecture,

hence, the memory interface packs and unpacks the data accessed accordingly.

Figure 10–1. Memory Address Spaces

‘C32

Strobe

control

registers

32-bit

CPU

PRGW pin

STRB0

STRB1

IOSTRB

Memory

interface

8-, 16-, 32-bit data in

8-, 16-, 32-bit-wide memory

Program in 16-, 32-bit-wide memory

8-, 16-, 32-bit data in

8-, 16-, 32-bit-wide memory

32-bit data in 32-bit-wide

memory

Program in 16-, 32-bit-wide memory

Program in 32-bit-wide memory

10.2.2 Program Memory Access

The ’C32 supports program execution from 16- or 32-bit external memory

width. The PRGW pin configures the width of the external program memory.

When this pin is pulled high, the ’C32 executes from 16-bit wide memory.

When this pin is pulled low, the ’C32 executes from 32-bit wide memory. For

16-bit wide zero wait-state memory, the ’C32 takes two instruction cycles to

fetch a single 32-bit instruction. During the first cycle the lower 16 bits of the

instruction are fetched. During the second cycle, the upper 16 bits are fetched

and concatenated with the lower 16 bits. 32-bit memory fetches are identical

to those of the ’C30 and ’C31.