Texas Instruments TMS320C3x User Manual

Page 431

DMA Controller

12-52

At reset, each DMA-channel control register is set to 0. This makes the DMA

channels lower-priority than the CPU, sets up the source address and destination

address to be calculated through linear addressing, and configures the DMA

channel in the unified mode.

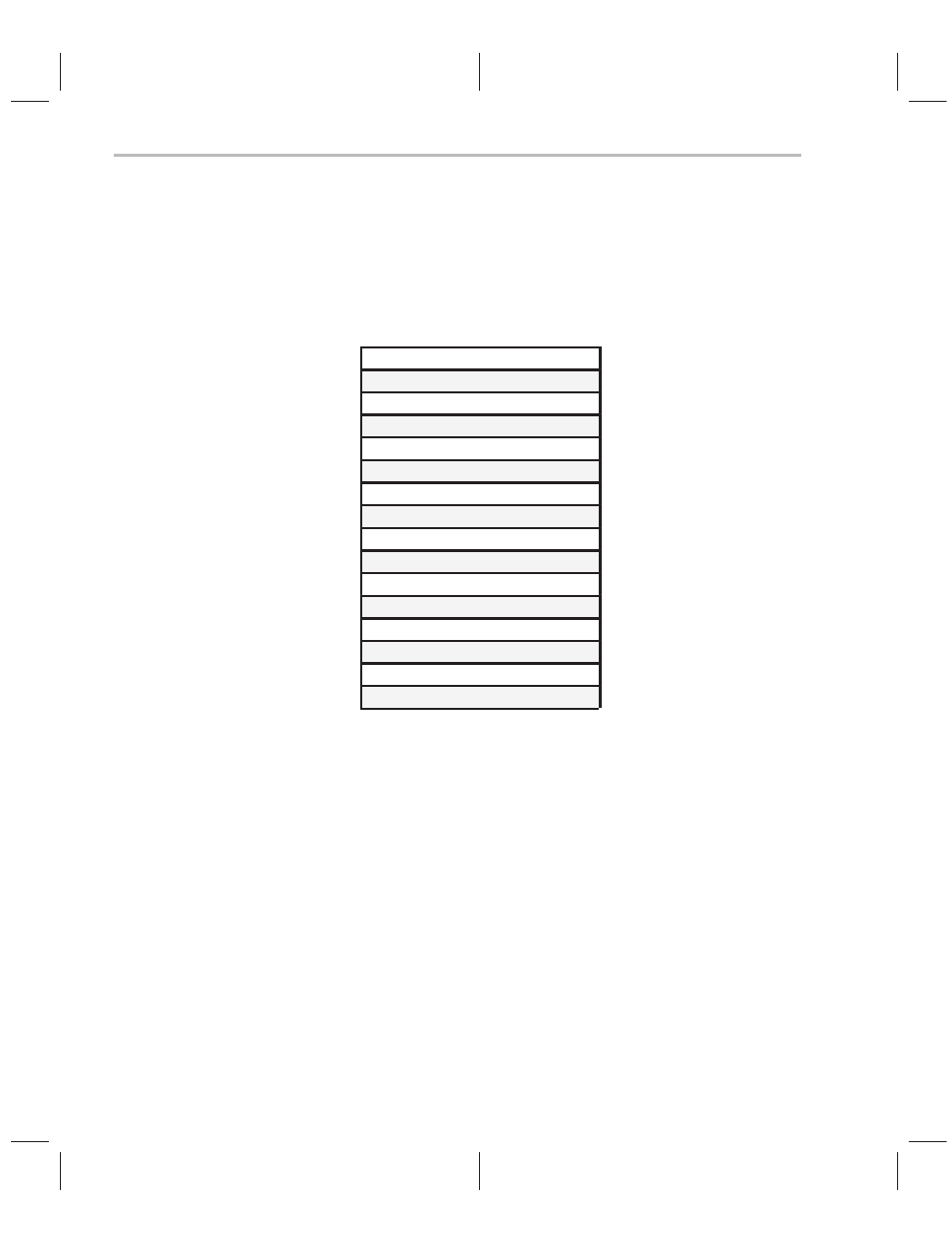

Figure 12–35. Memory-Mapped Locations for DMA Channels

БББББ

БББББ

Address

БББББББББББ

БББББББББББ

Register

Б

Б

БББББ

БББББ

808000h

БББББББББББ

БББББББББББ

DMA 0 global control

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

808004h

БББББББББББ

БББББББББББ

DMA 0 source address

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

808006h

БББББББББББ

БББББББББББ

DMA 0 destination address

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

808008h

БББББББББББ

БББББББББББ

DMA 0 transfer counter

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

808010h

БББББББББББ

БББББББББББ

DMA 1 global control†

Б

Б

БББББ

Б

БББББ

БББББ

808014h

БББББББББББ

БББББББББББ

DMA 1 source address†

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

808016h

БББББББББББ

БББББББББББ

DMA 1 destination address†

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

808018h

БББББББББББ

БББББББББББ

DMA 1 transfer counter†

Б

Б

БББББ

БББББ

Б

Б

БББББ

БББББ

БББББББББББ

БББББББББББ

Б

Б

† ’C32 only