Siemens S5-135U/155U User Manual

Page 282

6-20

System Manual

C79000-G8576-C199-06

CPUs in Operation

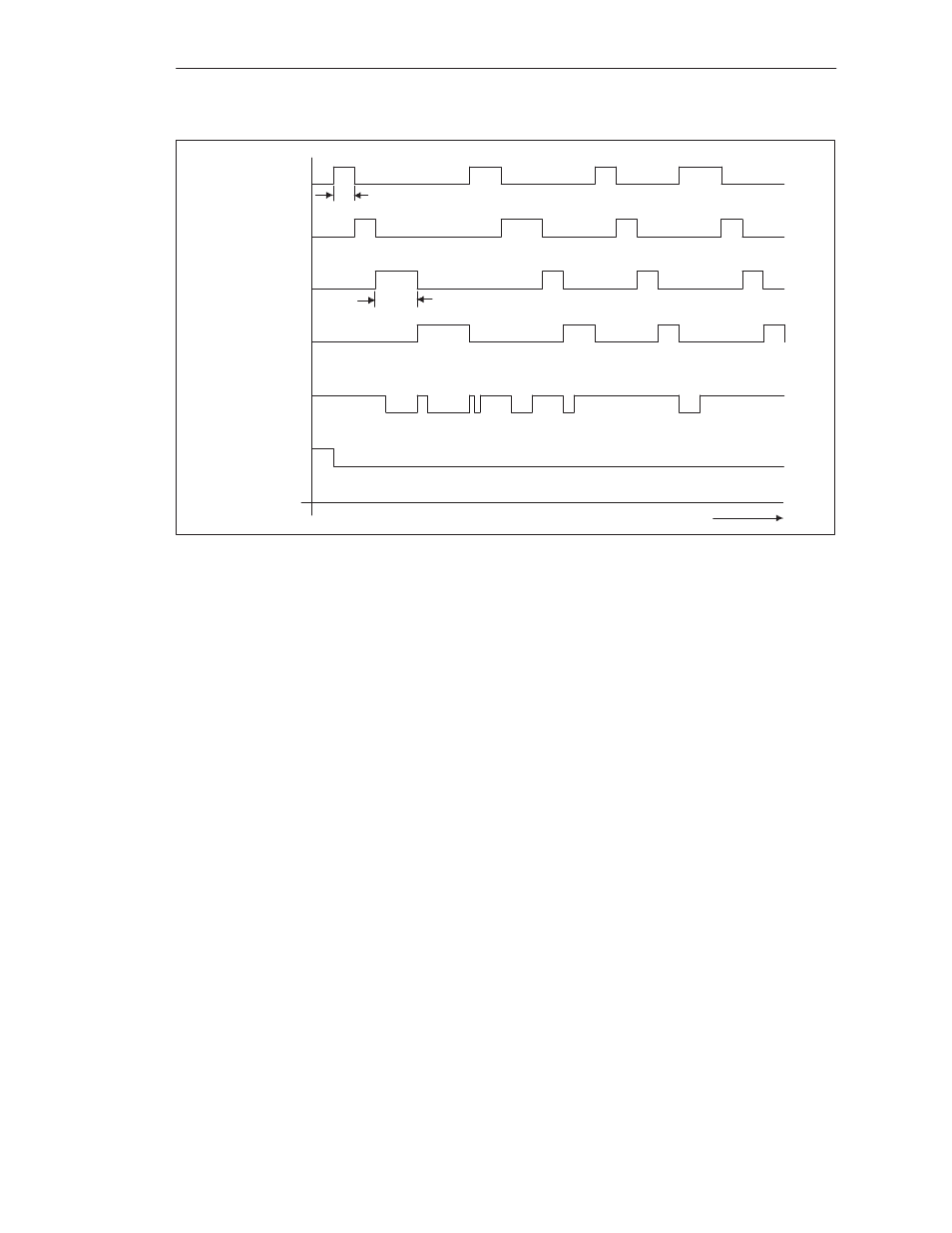

CPU1

CPU2

CPU3

CPU4

Bus Lock

Reset

Bus Enable for:

Time

Bus Lock

2

µ

s

2

µ

s +

Figure 6-7

Timing Sequences of the Bus Control Signals

Monitoring for continuous bus assignment

The bus lock signal can only be emitted by the CPU which has already

received a bus enable signal from the COR 923C. The bus enable time is

extended by the duration of the bus lock signal for the CPU (see Figure 6-7).

The factory setting for monitoring of the bus lock signal is 2 ms. If the signal

remains active for a longer duration, the COR 923C emits a signal which

results in a Stop of all CPUs.

The CPU which emitted the bus lock signal for too long a duration, is marked

by the CPU in a readable register under address FEFFH (fault register, see

Figure 6-8). The assigned BUS FAULT LED in the front plate of the COR

923C lights up. The register is cleared and the LED goes off again when the

signal which led to the Stop state becomes inactive.

Communication memory

The communication memory comprises a central battery-backed RAM in the

PLC. It has three areas: 1) the communication flags (256 bytes), 2) the

semaphores (32), and 3) four memory pages.

The communication flags are located in memory area F200H to F2FFH. The

communication flags enable the cyclic interchange of small volumes of data

between the CPUs in the S5-135U/155U PLC. The four memory pages serve

for the exchange of data blocks between CPUs.

Please consult the Programming Guides of the CPUs to program these two

functions.

Multiprocessor Operation/Coordinators