Siemens S5-135U/155U User Manual

Page 278

6-16

System Manual

C79000-G8576-C199-06

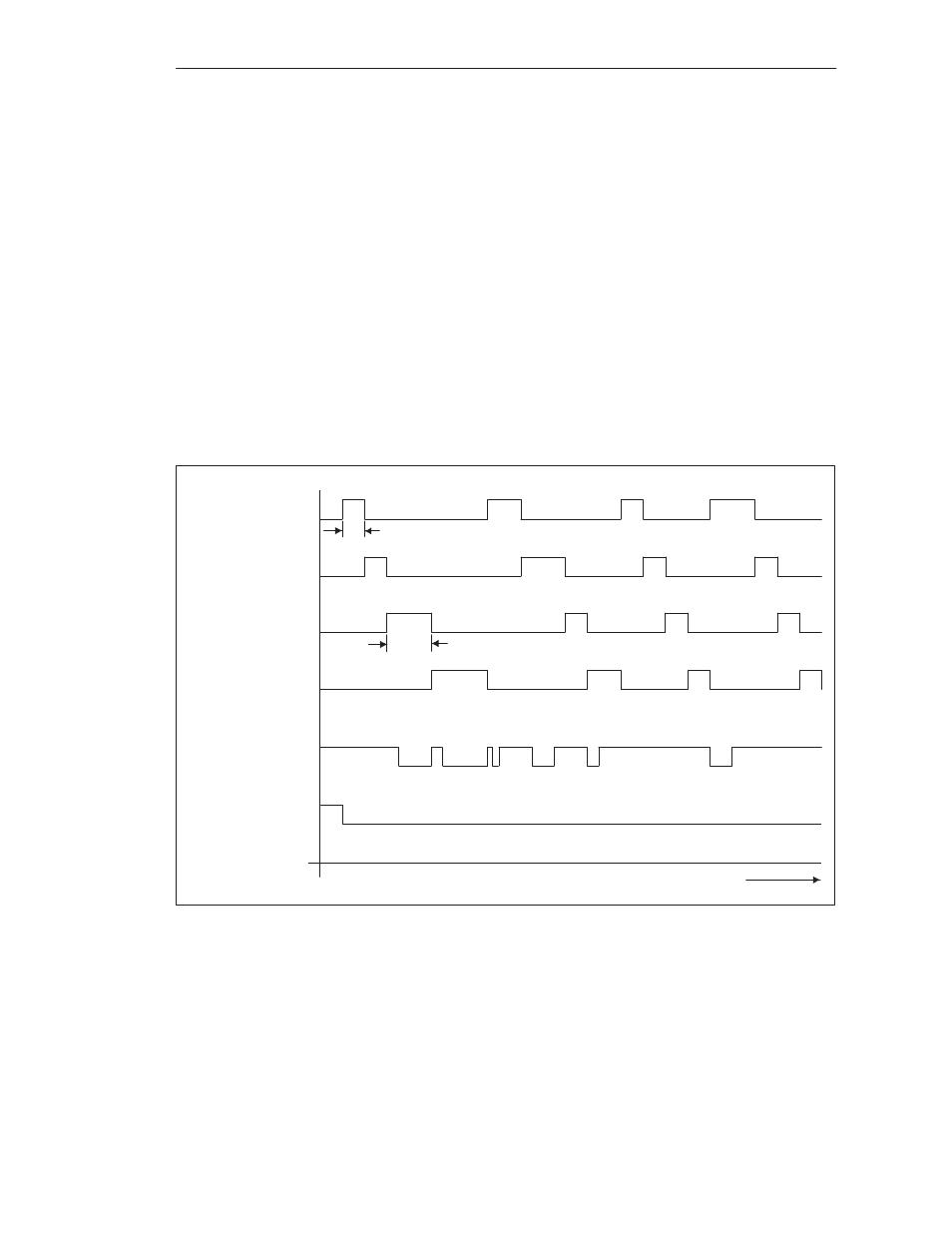

Bus arbitration

The COR 923A cyclically allocates a bus enable signal to each of the two to

four CPUs in the S5-135U/155U PLC. Only during this time can the relevant

CPU utilize the common S5 bus.

The assignment of bus enable signals takes place in time-division multiplex

operation. On the COR 923A, you set the number of CPUs with jumpers. The

enable time for access to the S5 bus is preset at 2 ms for all CPUs. If the bus

enable signal has been emitted by the coordinator for a CPU, this CPU can

extend the enable time with the bus lock signal. However, the user has no

influence on this.

The bus enable assignment sequence begins with CPU 1 after the

Reset signal is removed by the power supply, and enables the CPUs

in the following order according to the preset number of CPUs:

CPU 1, CPU 2, CPU 3, CPU 4, CPU 1, CPU 2 etc. (see Figure 6-5)

CPUs in Operation

CPU1

CPU2

CPU3

CPU4

Bus Lock

Reset

Bus Enable for:

Time

Bus Lock

2

µ

s

2

µ

s +

Figure 6-5

Timing Sequences of the Bus Signals

Communication memory

The communication memory comprises a central battery-backed RAM in the

PLC. It has two areas: the communication flags and the semaphores.

The communication flags on the COR 923A allow the cyclic interchange of

data between the CPUs. The semaphores are mainly used to coordinate the

exchange of data in the I/O area.

Principle of

Operation

Multiprocessor Operation/Coordinators