Maps and registers – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) User Manual

Page 145

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54H)

145

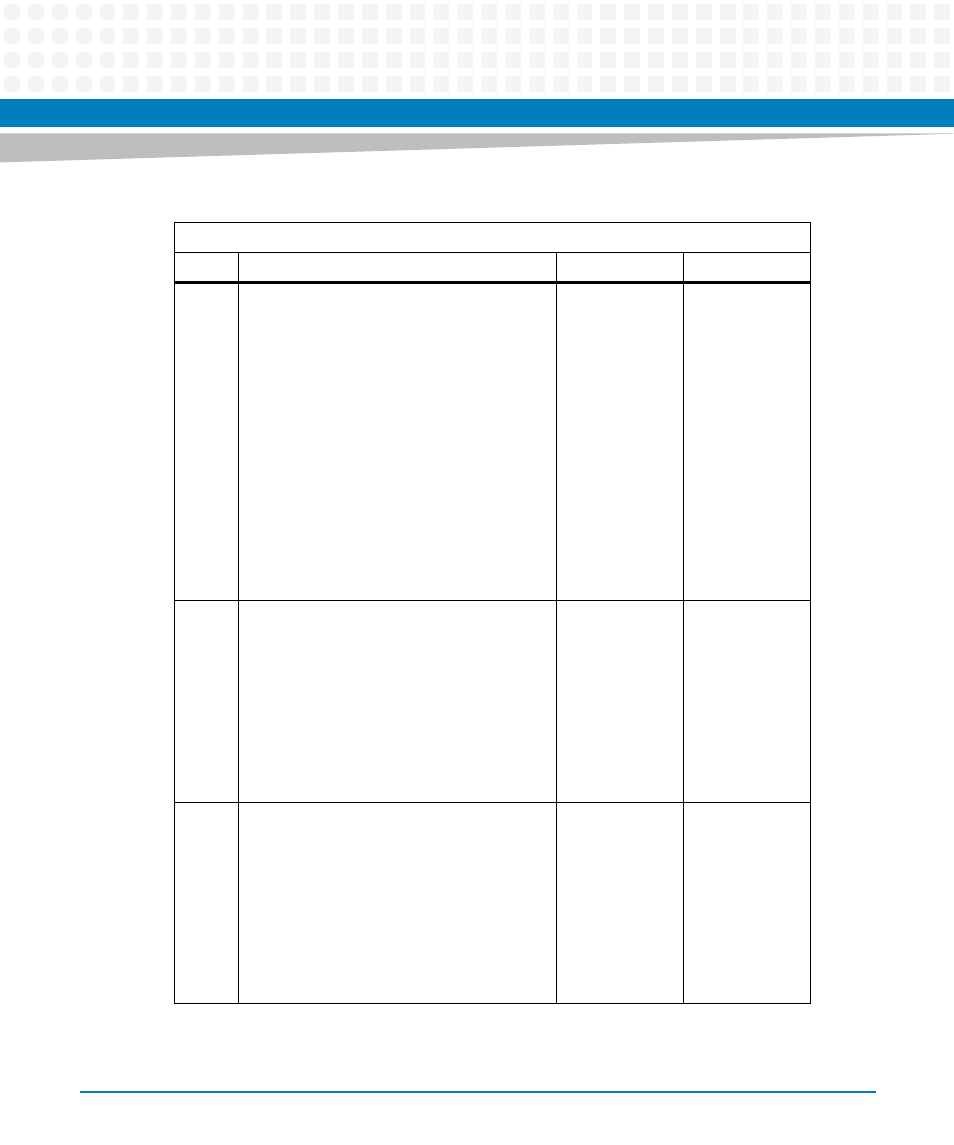

5

Transmit Holding Register Empty (THRE)

indicator

THRE is set when the THR is empty,

indicating that the ACE is ready to accept a

new character. If the THRE interrupt is

enabled when THRE is set, an interrupt is

generated. THRE is set when the contents of

the THR are transferred to the TSR. THRE is

cleared concurrent with the loading of the

THR by the CPU. In the FIFO mode, THRE is

set when the transmit FIFO is empty; it is

cleared when at least one byte is written to

the transmit FIFO:

1: THR/Transmit FIFO empty

0: THR/Transmit FIFO contains data

1

LPC: r

6

Transmitter Empty (TEMT) indicator

TEMT bit is set when the THR and the TSR are

both empty. When either the THR or the TSR

contains a data character, TEMT is cleared. In

the FIFO mode, TEMT is set when the

transmitter FIFO and shift register are both

empty:

1: THR/Transmit FIFO/TSR empty

0: THR/Transmit FIFO/TSR contains data

1

LPC: r

7

FIFO data error

In the FIFO mode, LSR7 is set when there is at

least one parity, framing, or break error in the

FIFO. It is cleared when the microprocessor

reads the LSR and there are no subsequent

errors in the FIFO. If FIFO is not used, bit

always reads 0:

1: FIFO data error encountered

0: No FIFO error encountered

0

LPC: r

Table 6-37 Line Status Register (LSR) (continued)

LPC IO Address: Base + 5

Bit

Description

Default

Access