2 apic (d31:f0) interrupt mapping, Table 6-3, Apic mode interrupt mapping – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) User Manual

Page 118: Maps and registers

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54H)

118

IRQ0, 1, 2, 8 and 13 must not be used for PCI interrupts (external inputs PIRQ [A…H]#, which

are only reserved for future usage) routing. If an interrupt is used for PCI IRQ [A:H], SCI or TCO

it must not be used for ISA (legacy)-style interrupts (via SERIRQ). In PIC Mode (8259 mode), PCI

interrupts are mapped to IRQ3-7,9-12, 14 or 15. If IRQ11 is used for Timer 2, software must

ensure that IRQ11 is not shared with any other devices to guarantee the proper operation of

Timer 2. The chipset does not prevent the sharing of IRQ11. Interrupts can individually be

programmed to be edge or level, except for IRQ0, IRQ2, IRQ8#, and IRQ13.

6.1.2

APIC (D31:F0) Interrupt Mapping

14

SATA

SATA Primary (legacy

mode), or via SERIRQ or

PIRQ#

15

SATA

SATA Secondary (legacy

mode), or via SERIRQ or

PIRQ#

Table 6-2 Non-APIC (PIC mode/8259 Mode) Interrupt Mapping (continued)

8259 IRQ

Typical Interrupt Source

Interrupt Source

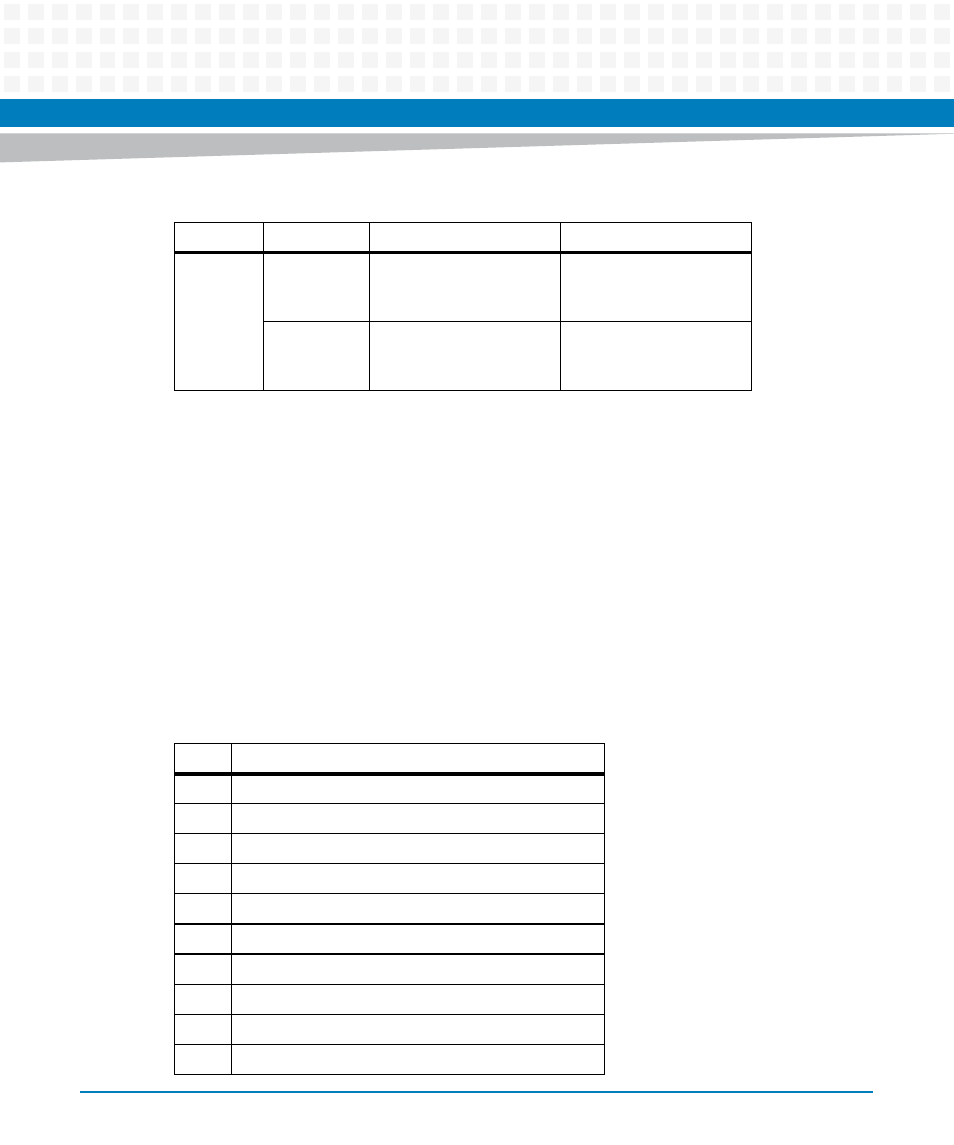

Table 6-3 APIC Mode Interrupt Mapping

IRQ

Interrupt Source

0

Cascade from 8259 1

1

Not Assigned

2

8254 Counter 0, Timer 0 (legacy mode)

3

Not Assigned

4

Not Assigned

5

Not Assigned

6

Not Assigned

7

Not Assigned

8

RTC, Timer 1 (legacy mode)

9

Option for TCI, TCO