3 non-maskable interrupt generation, Table 6-4, Nmi sources – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) User Manual

Page 120: Maps and registers

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54H)

120

6.1.3

Non-Maskable Interrupt Generation

The processor provides a single non-maskable interrupt pin (NMI), which has higher priority

than the maskable interrupt request pin (INTR). The NMI is used to activate a power failure

routine. The NMI is edge-triggered on a LOW-to-HIGH transition.The NMI is reset by setting the

corresponding NMI source enable/disable bit in the NMI Status and Control register (I/O

Register 61h).

The chipset can generate NMI by several sources which are described in following table.

The GPIO[15:0] can generate NMI. On the ATCA-7370, the GPIO3 of PCH connects to the

FPGA. The IPMC can request an NMI through controlling the GPIO3 of PCH connect to FPGA.

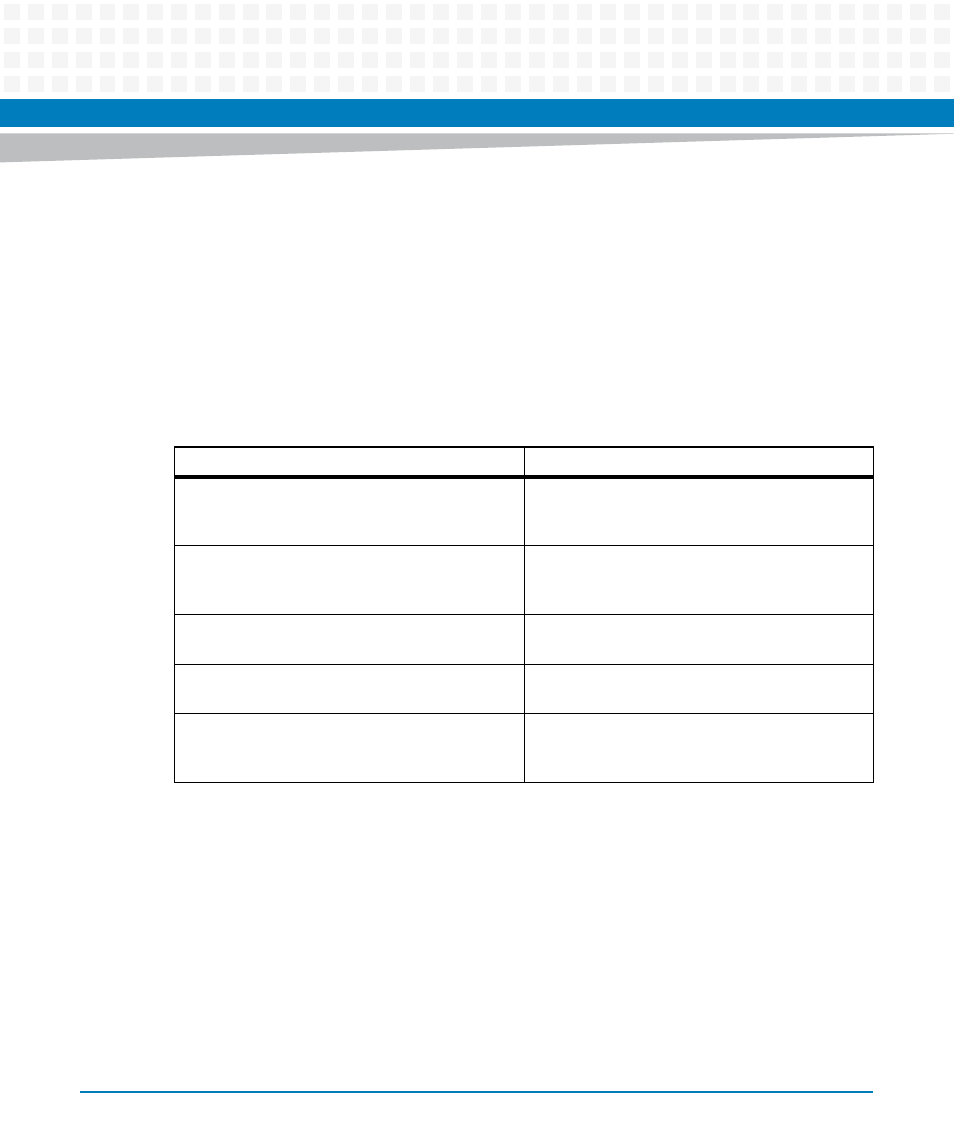

Table 6-4 NMI Sources

Cause of NMI

Comment

SERR# goes active (either internally, externally

using SERR# signal, or using message from

processor)

Can instead be routed to generate an SCI through

the NSI2SCI_EN bit (Device 31: Function 0, TCO

Base + 08h, Bit 11).

IOCHK# goes active using SERIRQ# stream (ISA

System Error)

Can instead be routed to generate an SCI through

the NMI2SCI_EN bit (Device 31: Function 0, TCO

Base + 08h, Bit 11).

SECSTS Register Device 31: Function F0 Offset

1Eh, Bit 8.

This is enabled by the Parity Error Response Bit

(PER) at Device 30: Function 0 Offset 04, Bit 6.

DEV_STS Register Device 31: Function F0 Offset

06h, Bit 8

No comment

GPIO[15:0] When configured as a General

Purpose input and routed as NMI (by GPIO_ROUT

at Device 31: Function 0 Offset B8)

No comment