2 transmitter holding register (thr), 3 interrupt enable register (ier), Table 6-29 – Artesyn ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) User Manual

Page 134: Transmitter holding register (thr) if dlab=0, Table 6-30, Interrupt enable register (ier) if dlab=0, Maps and registers

Maps and Registers

ATCA-7370/ATCA-7370-S Installation and Use (6806800P54H)

134

6.2.5.2

Transmitter Holding Register (THR)

This register holds the next data byte to be transmitted. When the transmit shift register

becomes empty, the contents of the THR is loaded into the shift register. The transmit data

request (TDRQ) bit in the line status register is set to one.

Writing to THR while in FIFO mode puts THR to the top. The data at the bottom of the FIFO is

loaded to the shift register when it is empty.

6.2.5.3

Interrupt Enable Register (IER)

This register enables four types of interrupts which independently activate the int signal and

sets a value in the Interrupt Identification Register (IIR). Each of the four interrupt types can be

disabled by resetting the appropriate bit of the IER register. Similarly, by setting the

appropriate bits, selected interrupts can be enabled.

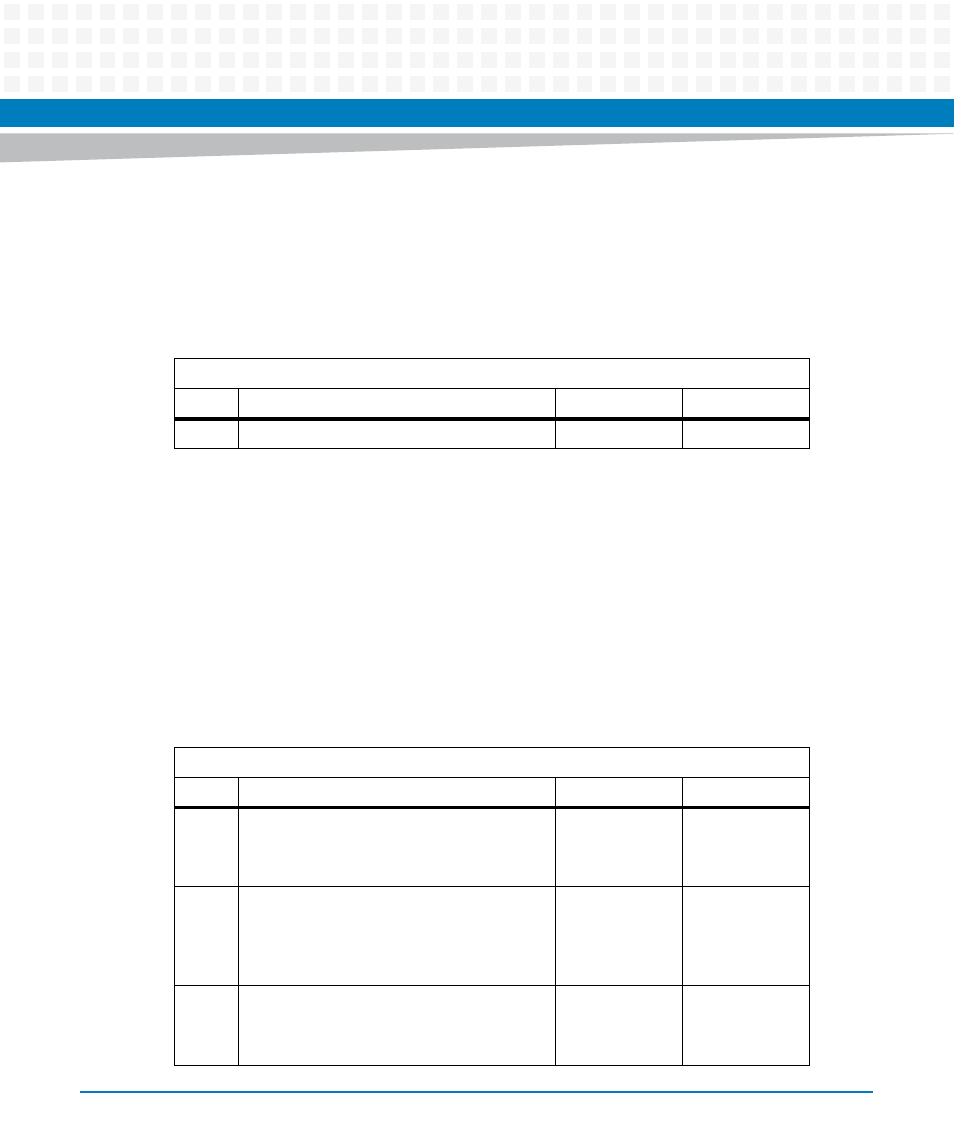

Table 6-29 Transmitter Holding Register (THR) if DLAB=0

LPC IO Address: Base

Bit

Description

Default

Access

7:0

Transmitter Holding register (THR)

Undef.

LPC: w

Table 6-30 Interrupt Enable Register (IER) if DLAB=0

LPC IO Address: Base + 1

Bit

Description

Default

Access

0

Receive data interrupt enable/disable:

1: receive data interrupt enabled

0: receive data interrupt disabled

0

LPC: r/w

1

Transmitter Holding Register Empty (THRE)

interrupt enable/disable

1: THRE interrupt enabled

0: THRE interrupt disabled

0

LPC: r/w

2

Receiver line status interrupt enable/disable

1: receiver line status interrupt enabled

0: receiver line status interrupt disabled

0

LPC: r/w