Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 99

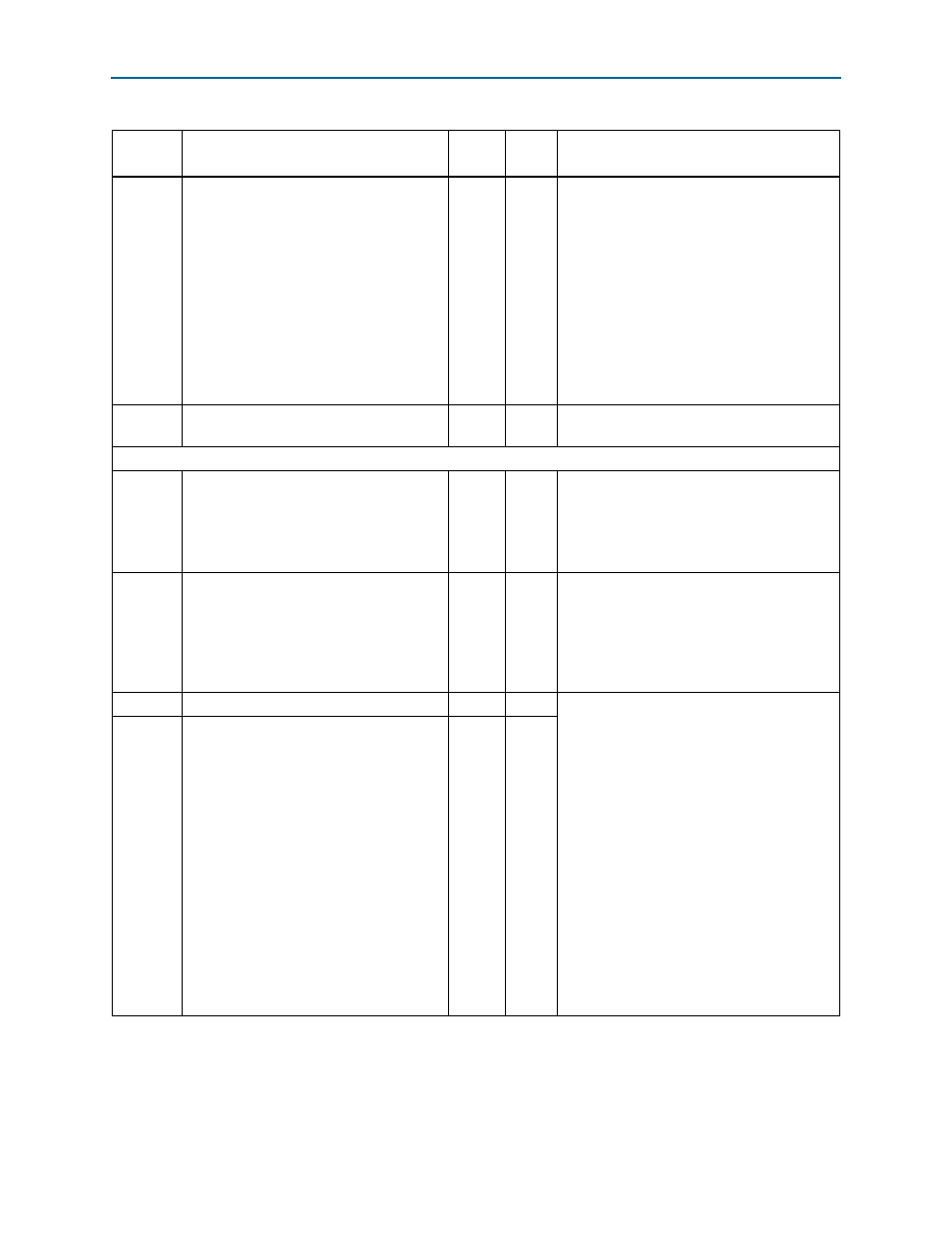

Chapter 8: Registers

8–5

MAC Registers

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

0x140

rx_preamble_inserter_control

RW

0x0

■

Bit 0 enables the preamble passthrough

mode on the receive datapath.

0—Disables the preamble passthrough

mode.

1—Enables the preamble passthrough

mode.

■

Bits 1 to 31 are reserved.

For more information on the XGMII

decapsulation in the preamble passthrough

mode, refer to

0x141 –

0x7FF

Reserved

—

—

Reserved for future use.

RX Frame Decoder (0x800:0xBFF)

0x800

rx_frame_control

RW

0x3

Specifies valid frame types, pause frames

handling, and use of supplementary

addresses.

Refer to

“Rx_frame_control Register” on

for the bit description.

0x801

rx_frame_maxlength

RW

1518

■

Bits 0 to 15 specify the maximum allowable

frame length. The MAC asserts the

avalon_st_rx_error[3]

signal when the

length of the receive frame exceeds the

value of this register.

■

Bits 16 to 31 are reserved.

0x802

rx_frame_addr0

RW

0x0

6-byte primary MAC address. You must map

the address to the registers in the following

manner:

■

rx_frame_addr0

= Last four bytes of the

address

■

rx_frame_addr1[

0:15]= First two bytes of

the address.

Bits 16 to 31 are reserved.

Example:

If the primary MAC address is 00-1C-23-17-

4A-CB, set rx_frame_addr0 to 0x23174ACB

and rx_frame_addr1 to 0x0000001C.

The IP core uses the primary MAC address to

filter unicast frames when the en_allucast

bit of the rx_frame_control register is set

to 0.

0x803

rx_frame_addr1

RW

0x0

Table 8–2. MAC Registers (Part 4 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description