10m-10gbe with ieee 1588v2 testbench, 10m-10gbe with ieee 1588v2 testbench components, 10m-10gbe with ieee 1588v2 testbench –5 – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 64

Chapter 6: 10M-10GbE MAC with IEEE 1588v2 Design Example

6–5

10M-10GbE with IEEE 1588v2 Testbench

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

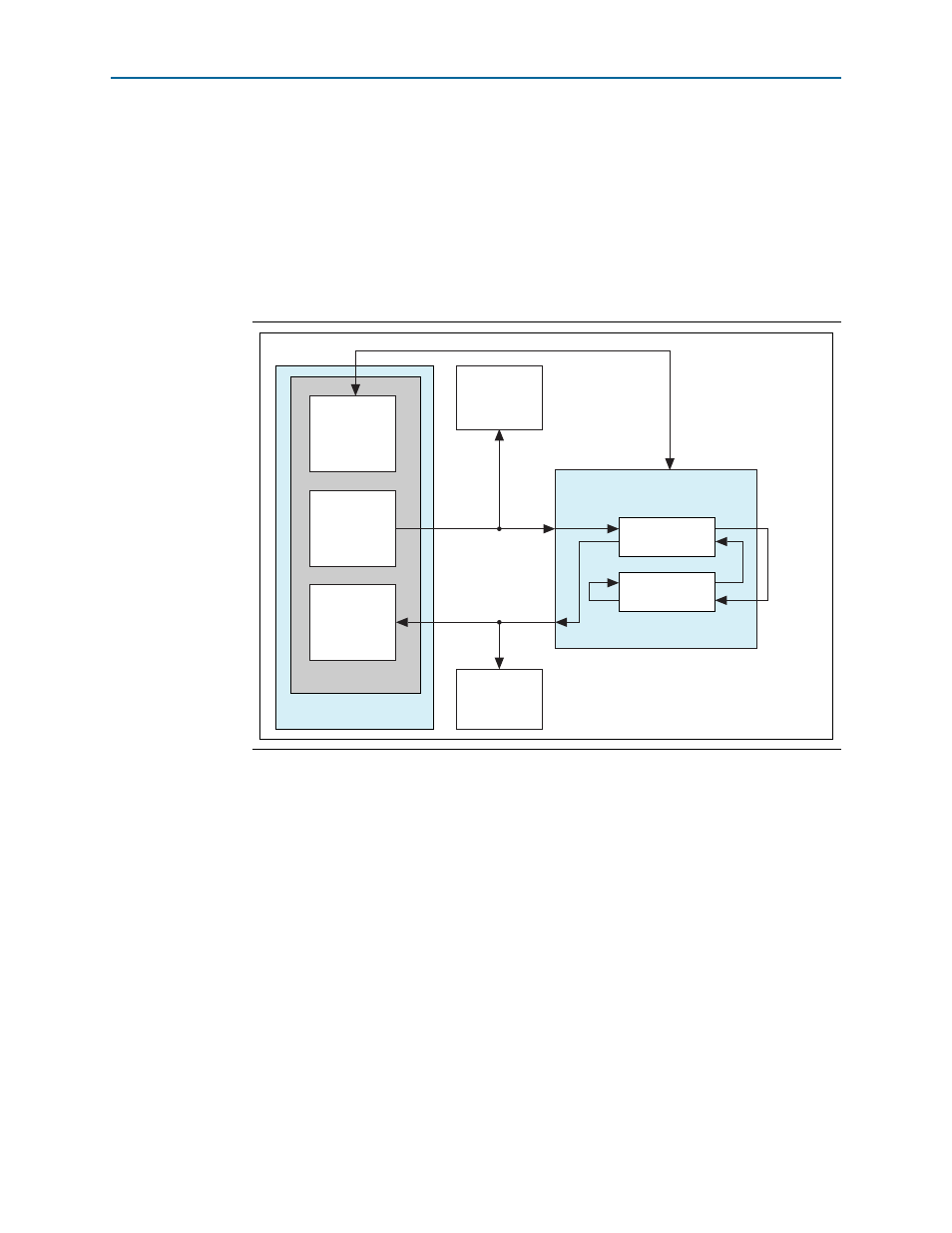

6.5. 10M-10GbE with IEEE 1588v2 Testbench

Altera provides testbench for you to verify the 10M-10GbE with IEEE 1588v2 design

example. The following sections describe the testbench, its components, and use.

6.5.1. 10M-10GbE with IEEE 1588v2 Testbench

The testbench operates in loopback mode.

Figure 6–3

shows the flow of the packets in

the design example.

6.5.2. 10M-10GbE with IEEE 1588v2 Testbench Components

The testbenches comprise the following modules:

■

Device under test (DUT)—the design example.

■

Avalon driver—uses Avalon-ST master bus functional models (BFMs) to exercise

the transmit and receive paths. The driver also uses the master Avalon-MM BFM

to access the Avalon-MM interfaces of the design example components.

■

Packet monitors—monitors the transmit and receive datapaths, and displays the

frames in the simulator console.

Figure 6–3. Testbench Block Diagram

Loopback

on Serial

Testbench

Avalon-MM

Ordinary Clock

Transparent Clock

Avalon-MM

Control

Register

Avalon-ST

Transmit

Frame

Generator

Avalon-ST

Receive

Frame

Monitor

Ethernet

Packet

Monitor

Ethernet

Packet

Monitor

DUT

avalon_bfm_wrapper.sv

Avalon Driver

Channel-0

Channel-1

Avalon-ST

Avalon-ST