10gbe design performance and resource utilization – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 37

Chapter 3: 10GbE MAC Design Examples

3–19

10GbE Design Example Compilation and Verification in Hardware

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

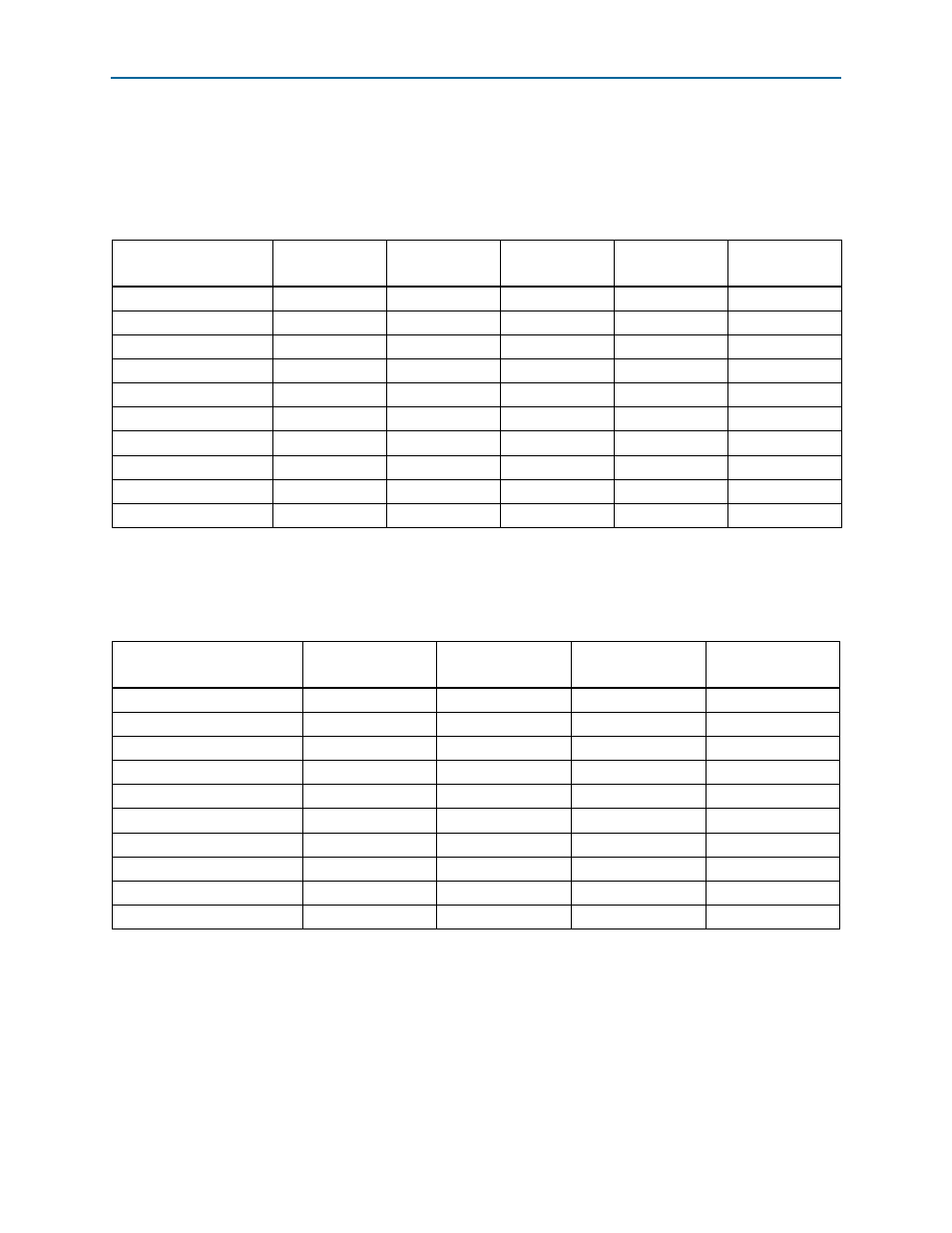

3.7.5. 10GbE Design Performance and Resource Utilization

provides the estimated performance and resource utilization of the 10GbE

design example obtained by compiling the design with the Quartus II software

targeting the Stratix IV GX (EP4SGX230KF40C2ES) device with speed grade –2.

provides the estimated performance and resource utilization of the 10GbE

design example obtained by compiling the design with the Quartus II software

targeting the Cyclone V GX (5CGXFC7D6F31C6) device with speed grade –6.

Table 3–7. Stratix IV Performance and Resource Utilization

Components

Combinational

ALUTs

Memory

ALUTs

Logic

Registers

Memory Block

(M9K)

f

MAX

(MHz)

MAC

4,054

36

4,710

6

156.25

Loopback

293

0

182

4

156.25

RX SC FIFO

231

0

210

5

156.25

TX SC FIFO

212

0

210

4

156.25

Hard XAUI PHY

1,892

0

1,215

0

156.25

MDIO

116

0

133

0

156.25

JTAG Master

523

0

440

1

156.25

Address Swapper

66

0

71

0

156.25

Qsys Fabric

993

2

1,018

0

156.25

Total Resource Utilization

7,840

38

8,019

20

156.25

Table 3–8. Cyclone V Performance and Resource Utilization

Components

Combinational

ALUTs

Logic Registers

Memory Block

(M10K)

f

MAX

(MHz)

MAC

4,417

5,464

6

156.25

Loopback

291

199

4

156.25

RX SC FIFO

242

231

4

156.25

TX SC FIFO

215

232

4

156.25

MDIO

118

144

0

156.25

Soft XAUI

1,642

1,750

3

156.25

JTAG Master

537

468

1

156.25

Address Swapper

66

71

0

156.25

Qsys Fabric

444

688

1

156.25

Total Resource Utilization

7,972

9,247

23

156.25