Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 102

8–8

Chapter 8: Registers

MAC Registers

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

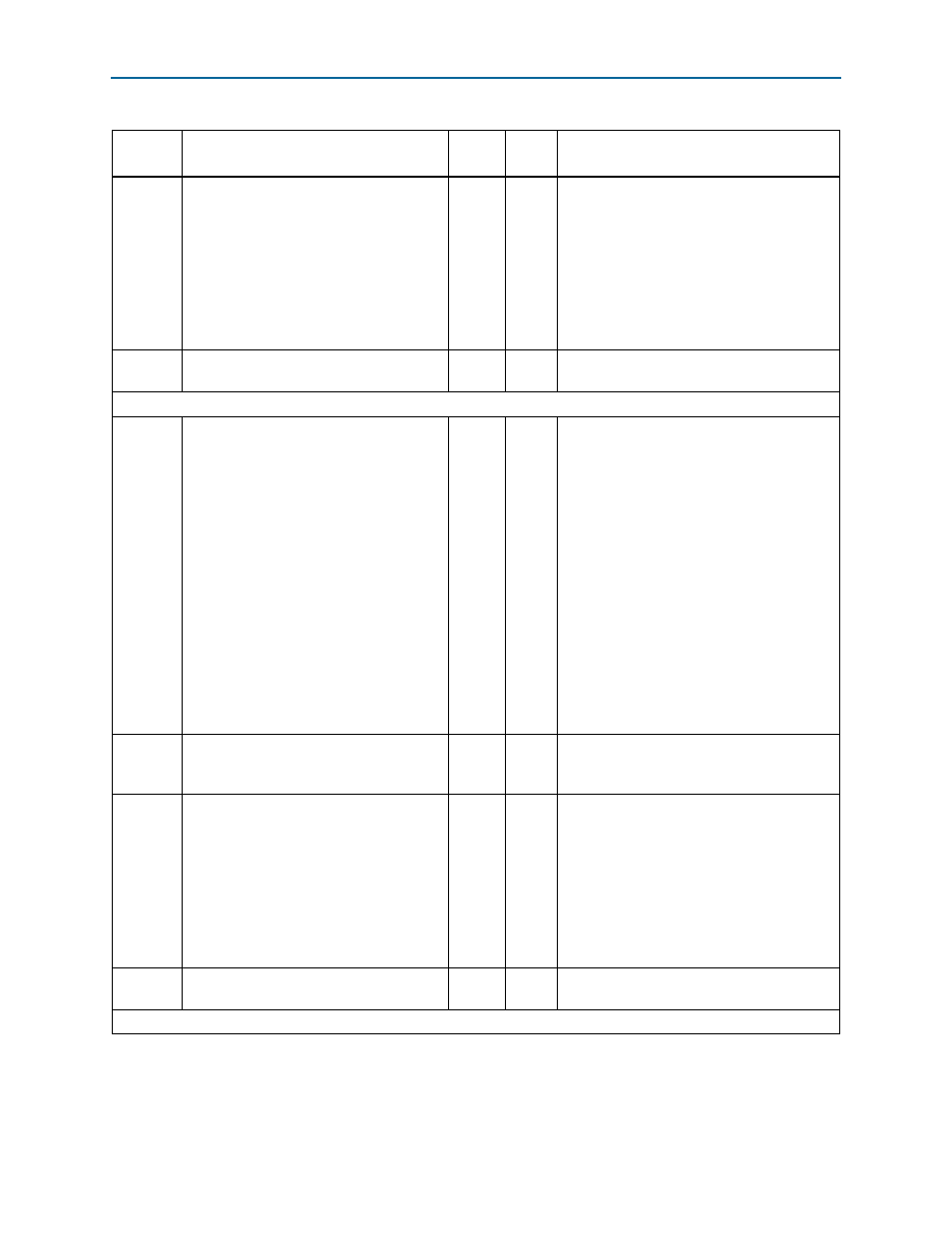

0x1100

tx_preamble_control

RW

0x0

■

Bit 0 configures the preamble passthrough

mode in the transmit datapath.

0—Set to 1 to disable the preamble

passthrough mode.

1—Set to 1 to enable the preamble

passthrough mode. MAC Tx identifies the

first 8-bytes of the client frame as

client-defined preamble.

■

Bits 1 to 31 are reserved.

0x1101 –

0x113F

Reserved

—

—

Reserved for future use.

TX Pause Frame Control and Generator (0x1140:0x117F)

0x1140

tx_pauseframe_control

RW

0x0

IEEE 802.3 pause frame generation.

■

Bit 0 configures the generation of XON

pause frames.

0—Disables pause frame generation.

1—Generates a pause frame with a pause

quanta value of 0.

■

Bit 1 configures the generation of XOFF

pause frames.

0—Disables pause frame generation.

1—Generates a pause frame using the

pause quanta specified in the

tx_pauseframe_quanta

register.

■

Bits 2 to 31 are reserved.

If both bits 0 and 1 are set to 1 simultaneously,

the IP core does not generate any pause

frames.

0x1141

tx_pauseframe_quanta

RW

0x0

16-bit pause quanta. The IP core uses this

value when it generates XOFF pause frames.

Bits 16 to 31 are reserved.

0x1142

tx_pauseframe_enable

RW

0x1

IEEE 802.3 pause frame generation process.

■

Bit 0 configures the process to generate the

IEEE 802.3 pause frame.

0—Disables pause frame generation

process.

1—Enables pause frame generation

process.

■

Bits 1 to 31 are reserved.

0x1143 –

0x117F

Reserved

—

—

Reserved for future use.

TX PFC Generator (0x1180:0x11FF)

Table 8–2. MAC Registers (Part 7 of 15)

Word

Offset

Register Name

Access

Reset

Value

Description