Clock and reset signals, Avalon-st transmit and receive interface signals – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 121

9–2

Chapter 9: Interface Signals

10-Gbps Ethernet MAC MegaCore Function User Guide

February 2014

Altera Corporation

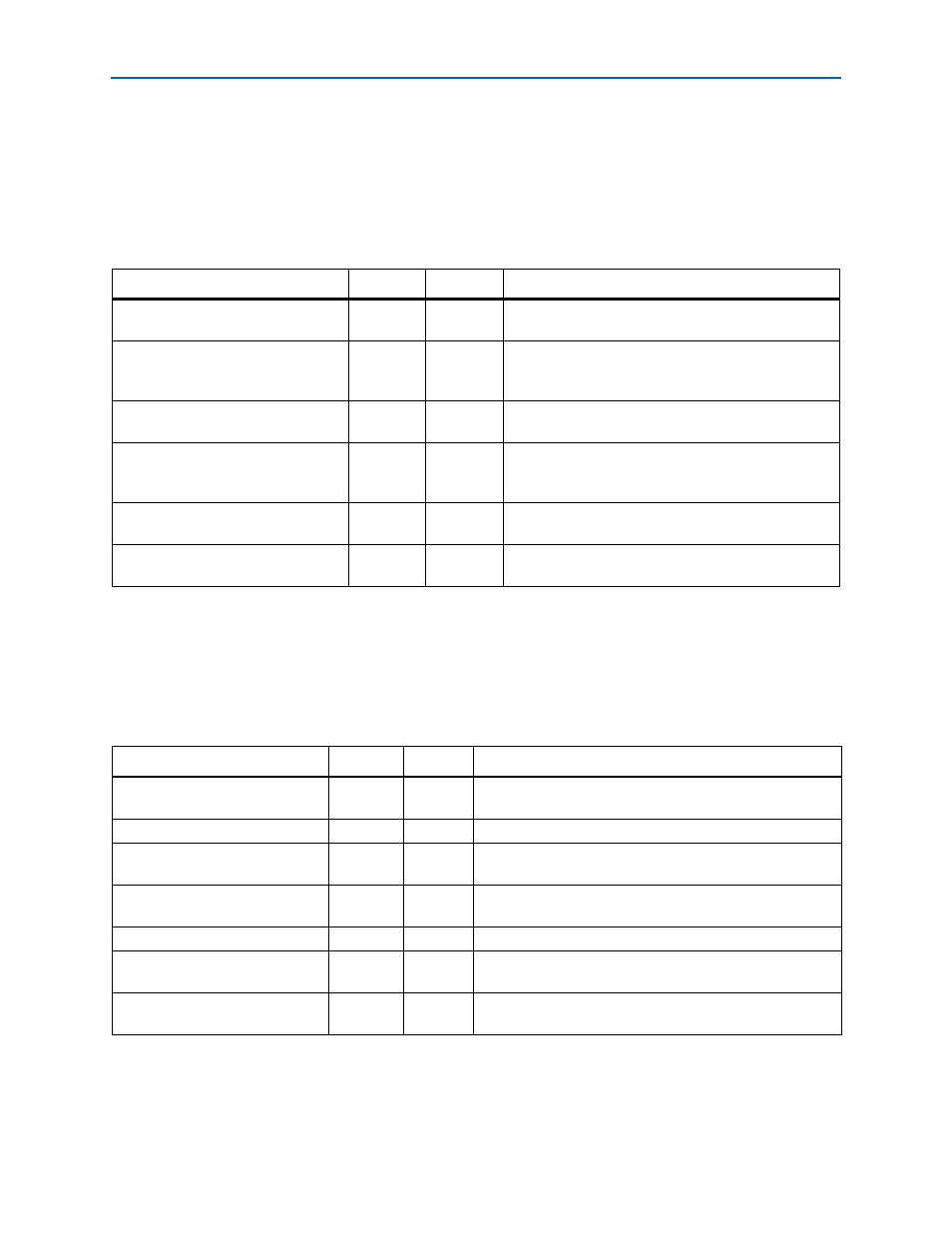

9.0.1. Clock and Reset Signals

The MAC operates in multiple clock domains. You can use different sources to drive

the clock and reset interfaces. Refer to

Table 9–1 on page 9–2

for the clock and timing

requirements for the clock and reset interfaces.

Table 9–1

lists the MAC clock and reset signals.

9.0.2. Avalon-ST Transmit and Receive Interface Signals

Table 9–2

describes the Avalon-ST transmit signals.

Table 9–1. Common Clock and Reset Signals

Signal

Direction

Width

Description

tx_clk_clk

Input

1

156.25-MHz transmit clock. Provides the timing

reference for the Avalon-ST transmit interface.

tx_reset_reset_n

Input

1

An active-low asynchronous reset signal for the

tx_clk_clk

domain. The MAC function implements a

reset synchronizer to generate a synchronous signal.

rx_clk_clk

Input

1

156.25-MHz receive clock. Provides the timing

reference for the Avalon-ST receive interface.

rx_reset_reset_n

Input

1

An active-low asynchronous reset signal for the

rx_clk_clk

domain. The MAC function implements a

reset synchronizer to generate a synchronous signal.

csr_clk_clk

Input

1

Configuration clock for the control and status interface.

The clock runs at 156.25-MHz or lower.

csr_reset_reset_n

Input

1

An active-low reset signal for the control and status

interface.

Note to

Table 9–1

:

(1) You can use the same clock source for both tx_clk_clk and rx_clk_clk.

Table 9–2. Avalon-ST Transmit Signals

Signal

Direction

Width

Description

avalon_st_tx_startofpacket

Input

1

Assert this signal to indicate the beginning of the transmit

packet.

avalon_st_tx_endofpacket

Input

1

Assert this signal to indicate the end of the transmit packet.

avalon_st_tx_valid

Input

1

Assert this signal to qualify the transmit data on the

avalon_st_tx_data

bus.

avalon_st_tx_ready

Output

1

When asserted, this signal indicates that the IP core is ready

to accept data.

avalon_st_tx_data[]

Input

64

Carries the transmit data from the client.

avalon_st_tx_empty[]

Input

3

Use this signal to specify the number of bytes that are empty

(not used) during cycles that contain the end of a packet.

avalon_st_tx_error

Input

1

Assert this signal to indicate the current receive packet

contains errors.