C. packet classifier, C.1. block diagram, Appendix c. packet classifier – Altera 10-Gbps Ethernet MAC MegaCore Function User Manual

Page 162: Appendix c, packet, Classifier

February 2014

Altera Corporation

10-Gbps Ethernet MAC MegaCore Function User Guide

C. Packet Classifier

The Packet Classifier decodes the packet types of incoming PTP packets and returns

the decoded information aligned with SOP to the 10GbE MAC IP.

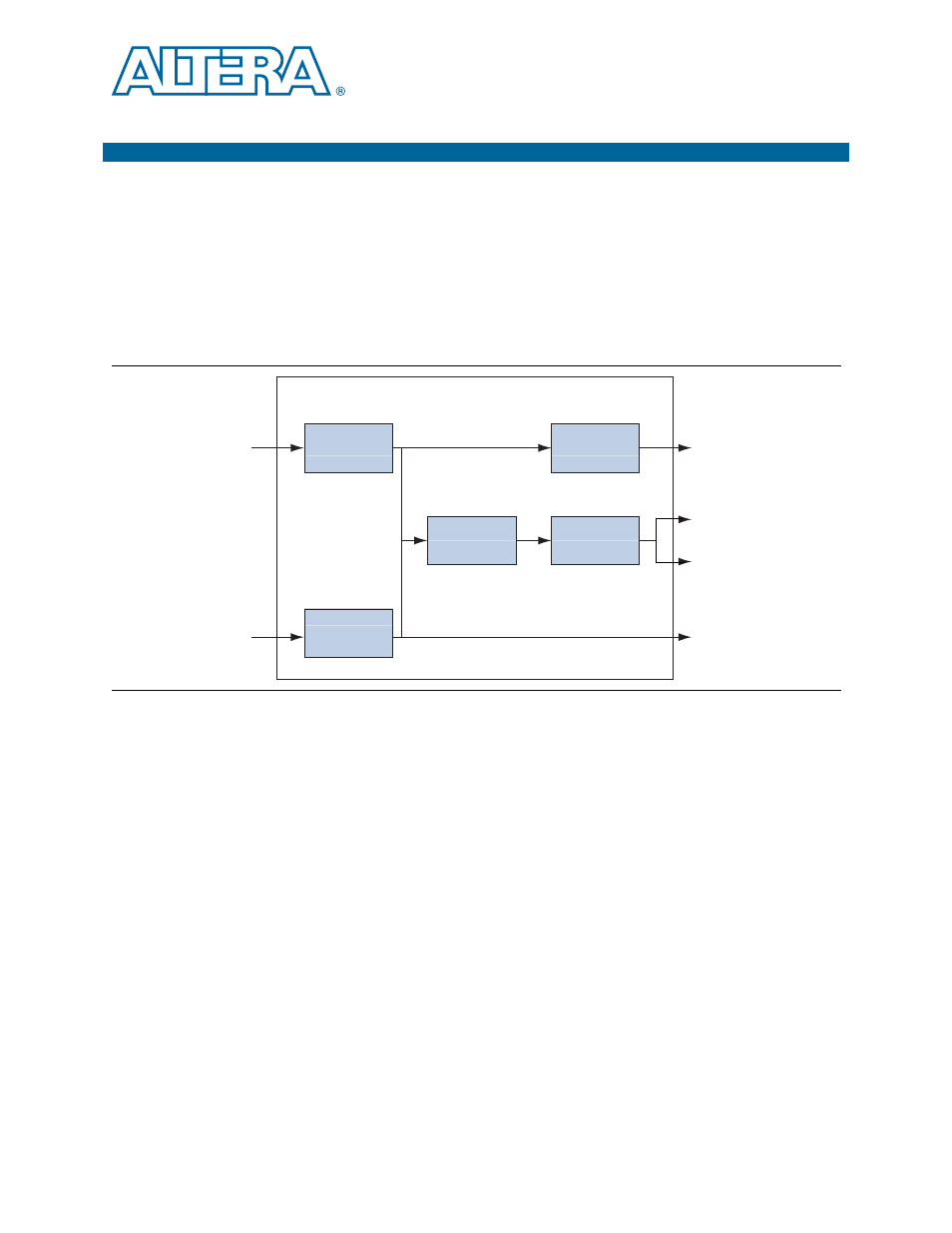

C.1. Block Diagram

Figure C–1

shows the block diagram for the Packet Classifier.

The Packet Classifier block diagram comprises the following components:

■

Data Pipeline—holds the data frame up to a specified number of cycles. The

number of cycles is determined by the largest length type field.

■

FIFO Packets—holds the Avalon-ST frame data.

■

FIFO Insert Control—the ingress control input bus that includes the signals

required for decoding logics and signals to the MAC that is required to be aligned

with SOP.

■

FIFO Request Control—contains decoded data such as control signals to inserter

and timestamp field locations.

■

Decoding—Decodes packet types of incoming PTP packets and returns the

decoded data to be stored in the FIFO request control block.

Figure C–1. Packet Classifier Block Diagram

Packet Classifier

Avalon-ST DataIn

(Sink)

Ingress Control

Input Signals

Ingress Control

Output Signals

Avalon-ST DataOut

(Source)

Control Signals to

Inserter

Timestamp Field

Location

Data Pipeline

FIFO Packets

FIFO Insert

Control

FIFO Request

Control

Decoding